# **CHAPTER 2**

Switched Mode Power Supplies

2.1 Using Power Semiconductors in Switched Mode Topologies (including transistor selection guides)

- 2.2 Output Rectification

- 2.3 Design Examples

- 2.4 Magnetics Design

- 2.5 Resonant Power Supplies

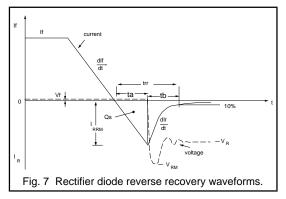

# Using Power Semiconductors in Switched Mode Topologies

# 2.1.1 An Introduction to Switched Mode Power Supply Topologies

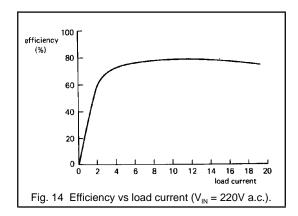

For many years the world of power supply design has seen a gradual movement away from the use of linear power supplies to the more practical switched mode power supply (S.M.P.S.). The linear power supply contains a mains transformer and a dissipative series regulator. This means the supply has extremely large and heavy 50/60 Hz transformers, and also very poor power conversion efficiencies, both serious drawbacks. Typical efficiencies of 30% are standard for a linear. This compares with efficiencies of between 70 and 80%, currently available using S.M.P.S. designs.

Furthermore, by employing high switching frequencies, the sizes of the power transformer and associated filtering components in the S.M.P.S. are dramatically reduced in comparison to the linear. For example, an S.M.P.S. operating at 20kHz produces a 4 times reduction in component size, and this increases to about 8 times at 100kHz and above. This means an S.M.P.S. design can produce very compact and lightweight supplies. This is now an essential requirement for the majority of electronic systems. The supply must slot into an ever shrinking space left for it by electronic system designers.

#### Outline

At the heart of the converter is the high frequency inverter section, where the input supply is chopped at very high frequencies (20 to 200kHz using present technologies) then filtered and smoothed to produce dc outputs. The circuit configuration which determines how the power is

transferred is called the TOPOLOGY of the S.M.P.S., and is an extremely important part of the design process. The topology consists of an arrangement of transformer, inductors, capacitors and power semiconductors (bipolar or MOSFET power transistors and power rectifiers).

Presently, there is a very wide choice of topologies available, each one having its own particular advantages and disadvantages, making it suitable for specific power supply applications. Basic operation, advantages, drawbacks and most common areas of use for the most common topologies are discussed in the following sections. A selection guide to the Philips range of power semiconductors (including bipolars, MOSFETs and rectifiers) suitable for use in S.M.P.S. applications is given at the end of each section.

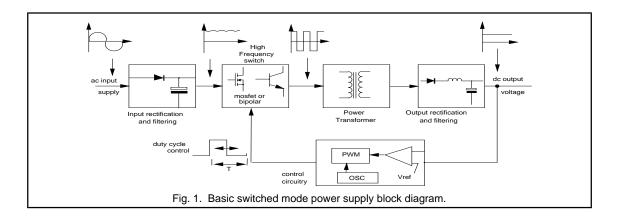

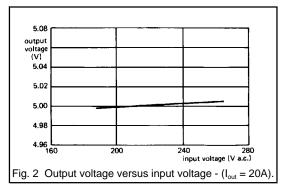

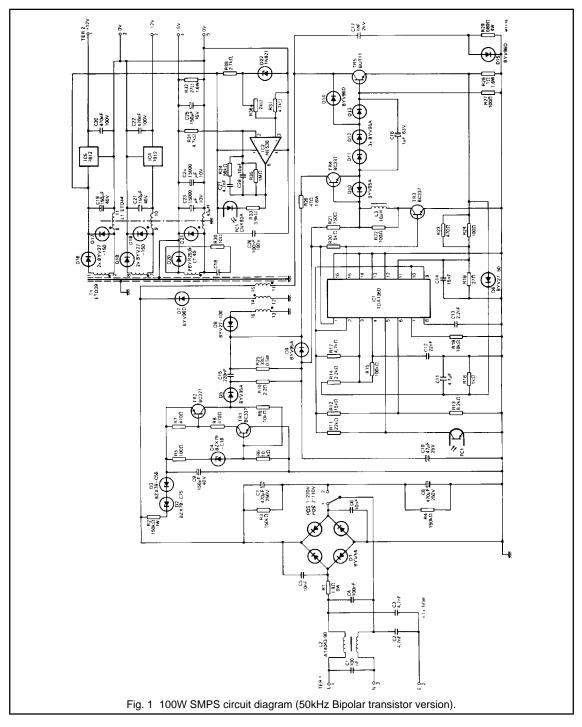

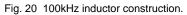

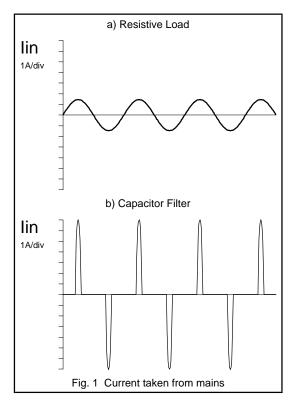

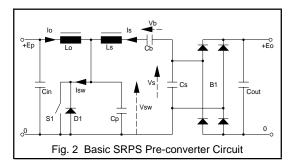

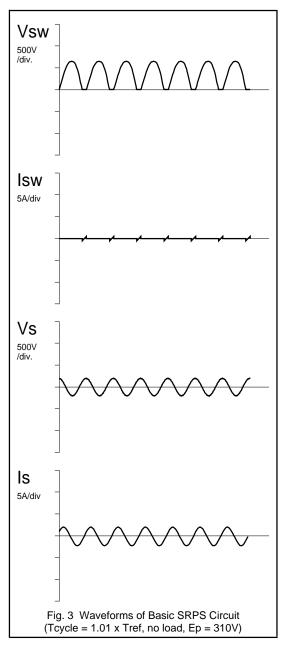

## (1) Basic switched mode supply circuit.

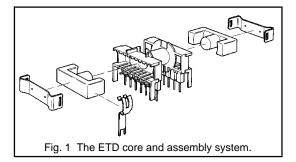

An S.M.P.S. can be a fairly complicated circuit, as can be seen from the block diagram shown in Fig. 1. (This configuration assumes a 50/60Hz mains input supply is used.) The ac supply is first rectified, and then filtered by the input reservoir capacitor to produce a rough dc input supply. This level can fluctuate widely due to variations in the mains. In addition the capacitance on the input has to be fairly large to hold up the supply in case of a severe droop in the mains. (The S.M.P.S. can also be configured to operate from any suitable dc input, in this case the supply is called a dc to dc converter.)

The unregulated dc is fed directly to the central block of the supply, the high frequency power switching section. Fast switching power semiconductor devices such as MOSFETs and Bipolars are driven on and off, and switch the input voltage across the primary of the power transformer. The drive pulses are normally fixed frequency (20 to 200kHz) and variable duty cycle. Hence, a voltage pulse train of suitable magnitude and duty ratio appears on the transformer secondaries. This voltage pulse train is appropriately rectified, and then smoothed by the output filter, which is either a capacitor or capacitor / inductor arrangement, depending upon the topology used. This transfer of power has to be carried out with the lowest losses possible, to maintain efficiency. Thus, optimum design of the passive and magnetic components, and selection of the correct power semiconductors is critical.

Regulation of the output to provide a stabilised dc supply is carried out by the control / feedback block. Generally, most S.M.P.S. systems operate on a fixed frequency pulse width modulation basis, where the duration of the on time of the drive to the power switch is varied on a cycle by cycle basis. This compensates for changes in the input supply and output load. The output voltage is compared to an accurate reference supply, and the error voltage produced by the comparator is used by dedicated control logic to terminate the drive pulse to the main power switch/switches at the correct instance. Correctly designed, this will provide a very stable dc output supply.

It is essential that delays in the control loop are kept to a minimum, otherwise stability problems would occur. Hence, very high speed components must be selected for the loop. In transformer-coupled supplies, in order to keep the isolation barrier intact, some type of electronic isolation is required in the feedback. This is usually achieved by using a small pulse transformer or an opto-isolator, hence adding to the component count.

In most applications, the S.M.P.S. topology contains a power transformer. This provides isolation, voltage scaling through the turns ratio, and the ability to provide multiple outputs. However, there are non-isolated topologies (without transformers) such as the buck and the boost converters, where the power processing is achieved by inductive energy transfer alone. All of the more complex arrangements are based on these non-isolated types.

#### (2) Non-Isolated converters.

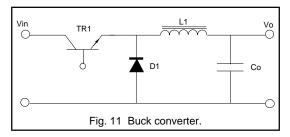

The majority of the topologies used in today's converters are all derived from the following three non-isolated versions called the buck, the boost and the buck-boost. These are the simplest configurations possible, and have the lowest component count, requiring only one inductor, capacitor, transistor and diode to generate their single output. If isolation between the input and output is required, a transformer must be included before the converter.

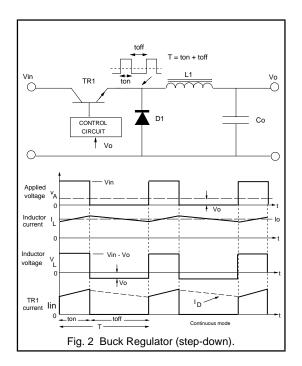

#### (a) The Buck converter.

The forward converter family which includes the push-pull and bridge types, are all based on the buck converter, shown in Fig. 2. Its operation is straightforward. When switch TR1 is turned on, the input voltage is applied to inductor L1 and power is delivered to the output. Inductor current also builds up according to Faraday's law shown below:-

$$V = L \frac{dI}{dt}$$

When the switch is turned off, the voltage across the inductor reverses and freewheel diode D1 becomes forward biased. This allows the energy stored in the inductor to be delivered to the output. This continuous current is then smoothed by output capacitor Co. Typical buck waveforms are also shown in Fig. 2.

The LC filter has an averaging effect on the applied pulsating input, producing a smooth dc output voltage and current, with very small ripple components superimposed. The average voltage/sec across the inductor over a complete switching cycle must equal zero in the steady state. (The same applies to all of the regulators that will be discussed.)

Neglecting circuit losses, the average voltage at the input side of the inductor is  $V_{in}D$ , while  $V_o$  is the output side voltage. Thus, in the steady state, for the average voltage across the inductor to be zero, the basic dc equation of the buck is simply:-

$$\frac{V_o}{V_i} = D$$

D is the transistor switch duty cycle, defined as the conduction time divided by one switching period, usually expressed in the form shown below:-

$$D = \frac{t_{on}}{T};$$

where  $T = t_{on} + t_{off}$

Thus, the buck is a stepdown type, where the output voltage is always lower than the input. (Since D never reaches one.) Output voltage regulation is provided by varying the duty cycle of the switch. The LC arrangement provides very effective filtering of the inductor current. Hence, the buck and its derivatives all have very low output ripple characteristics. The buck is normally always operated in continuous mode ( inductor current never falls to zero) where peak currents are lower, and the smoothing capacitor requirements are smaller. There are no major control problems with the continuous mode buck.

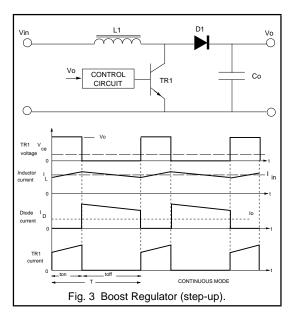

#### (b) The Boost Converter.

Operation of another fundamental regulator, the boost, shown in Fig. 3 is more complex than the buck. When the switch is on, diode D1 is reverse biased, and  $V_{in}$  is applied across inductor, L1. Current builds up in the inductor to a peak value, either from zero current in a discontinuous mode, or an initial value in the continuous mode. When the switch turns off, the voltage across L1 reverses, causing the voltage at the diode to rise above the input voltage. The diode then conducts the energy stored in the inductor, plus energy direct from the supply to the smoothing capacitor and load. Hence,  $V_o$  is always greater than  $V_{in}$ , making this a stepup converter. For continuous mode operation, the boost dc equation is obtained by a similar process as for the buck, and is given below:-

$$\frac{V_o}{V_i} = \frac{1}{1-D}$$

Again, the output only depends upon the input and duty cycle. Thus, by controlling the duty cycle, output regulation is achieved.

From the boost waveforms shown in Fig. 3, it is clear that the current supplied to the output smoothing capacitor from the converter is the diode current, which will always be discontinuous. This means that the output capacitor must be large, with a low equivalent series resistance (e.s.r) to produce a relatively acceptable output ripple. This is in contrast to the buck output capacitor requirements described earlier. On the other hand, the boost input current is the continuous inductor current, and this provides low input ripple characteristics. The boost is very popular for capacitive load applications such as photo-flashers and battery chargers. Furthermore, the continuous input current makes the boost a popular choice as a pre-regulator, placed before the main converter. The main functions being to regulate the input supply, and to greatly improve the line power factor. This requirement has become very important in recent years, in a concerted effort to improve the power factor of the mains supplies.

If the boost is used in discontinuous mode, the peak transistor and diode currents will be higher, and the output capacitor will need to be doubled in size to achieve the same output ripple as in continuous mode. Furthermore, in discontinuous operation, the output voltage also becomes dependent on the load, resulting in poorer load regulation.

Unfortunately, there are major control and regulation problems with the boost when operated in continuous mode. The pseudo LC filter effectively causes a complex second order characteristic in the small signal (control) response. In the discontinuous mode, the energy in the inductor at the start of each cycle is zero. This removes the inductance from the small signal response, leaving only the output capacitance effect. This produces a much simpler response, which is far easier to compensate and control.

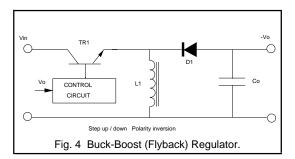

# (c) The Buck-Boost Regulator (Non-isolated Flyback).

The very popular flyback converter (see section 5(a)) is not actually derived solely from the boost. The flyback only delivers stored inductor energy during the switch off-time. The boost, however, also delivers energy from the input. The flyback is actually based on a combined topology of the previous two, called the buck-boost or non isolated flyback regulator. This topology is shown in Fig. 4.

When the switch is on, the diode is reverse biased and the input is connected across the inductor, which stores energy as previously explained. At turn-off, the inductor voltage reverses and the stored energy is then passed to the capacitor and load through the forward biased rectifier diode.

The waveforms are similar to the boost except that the transistor switch now has to support the sum of Vin and Vo across it. Clearly, both the input and output currents must be discontinuous. There is also a polarity inversion, the output voltage generated is negative with respect to the input. Close inspection reveals that the continuous mode dc transfer function is as shown below:-

$$\frac{V_o}{V_i} = \frac{D}{1-D}$$

Observation shows that the value of the switch duty ratio, D can be selected such that the output voltage can either be higher or lower than the input voltage. This gives the converter the flexibility to either step up or step down the supply.

This regulator also suffers from the same continuous mode control problems as the boost, and discontinuous mode is usually favoured.

Since both input and output currents are pulsating, low ripple levels are very difficult to achieve using the buck-boost. Very large output filter capacitors are needed, typically up to 8 times that of a buck regulator.

The transistor switch also needs to be able to conduct the high peak current, as well as supporting the higher summed voltage. The flyback regulator (buck-boost) topology places the most stress on the transistor. The rectifier diode also has to carry high peak currents and so the r.m.s conduction losses will be higher than those of the buck.

## (3) Transformers in S.M.P.S. converters.

The non-isolated versions have very limited use, such as dc-dc regulators only capable of producing a single output. The output range is also limited by the input and duty cycle. The addition of a transformer removes most of these constraints and provides a converter with the following advantages:-

1) Input to output isolation is provided. This is normally always necessary for 220/110 V mains applications, where a degree of safety is provided for the outputs.

2) The transformer turns ratio can be selected to provide outputs widely different from the input; non-isolated versions are limited to a range of approximately 5 times. By selecting the correct turns ratio, the duty cycle of the converter can also be optimised and the peak currents flowing minimised. The polarity of each output is also selectable, dependent upon the polarity of the secondary w.r.t the primary.

3) Multiple outputs are very easily obtained, simply by adding more secondary windings to the transformer.

There are some disadvantages with transformers, such as their additional size, weight and power loss. The generation of voltage spikes due to leakage inductance may also be a problem.

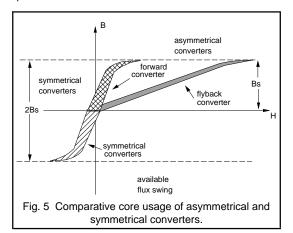

The isolated converters to be covered are split into two main categories, called asymmetrical and symmetrical converters, depending upon how the transformer is operated.

In asymmetrical converters the magnetic operating point of the transformer is always in one quadrant i.e the flux and the magnetic field never changes sign. The core has to be reset each cycle to avoid saturation, meaning that only half of the usable flux is ever exploited. This can be seen in Fig. 5, which shows the operating mode of each converter. The flyback and forward converter are both asymmetrical types. The diagram also indicates that the flyback converter is operated at a lower permeability (B/H) and lower inductance than the others. This is because the flyback transformer actually stores all of the energy before dumping into the load, hence an air gap is required to store this energy and avoid core saturation. The air gap has the effect of reducing the overall permeability of the core. All of the other converters have true transformer action and ideally store no energy, hence, no air gap is needed.

In the symmetrical converters which always require an even number of transistor switches, the full available flux swing in both quadrants of the B / H loop is used, thus utilising the core much more effectively. Symmetrical converters can therefore produce more power than their asymmetrical cousins. The 3 major symmetrical topologies used in practice are the push-pull, the half-bridge and the full bridge types.

Table 1 outlines the typical maximum output power available from each topology using present day technologies:-

| Converter Topology                  | Typical max output power |

|-------------------------------------|--------------------------|

| Flyback                             | 200W                     |

| Forward                             | 300W                     |

| Two transistor forward /<br>flyback | 400W                     |

| Push-pull                           | 500W                     |

| Half-Bridge                         | 1000W                    |

| Full-Bridge                         | >1000W                   |

Table 1. Converter output power range.

Many other topologies exist, but the types outlined in Table 1 are by far the most commonly used in present S.M.P.S. designs. Each is now looked at in more detail, with a selection guide for the most suitable Philips power semiconductors included.

# (4) Selection of the power semiconductors.

#### The Power Transistor.

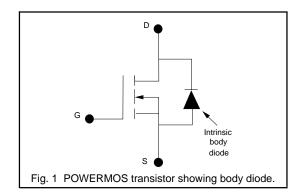

The two most common power semiconductors used in the S.M.P.S. are the Bipolar transistor and the power MOSFET. The Bipolar transistor is normally limited to use at frequencies up to 30kHz, due to switching loss. However, it has very low on-state losses and is a relatively cheap device, making it the most suitable for lower frequency applications. The MOSFET is selected for higher frequency operation because of its very fast switching speeds, resulting in low (frequency dependent) switching losses. The driving of the MOSFET is also far simpler and less expensive than that required for the Bipolar. However, the on-state losses of the MOSFET are far higher than the Bipolar, and they are also usually more expensive. The selection of which particular device to use is normally a compromise between the cost, and the performance required.

#### (i) Voltage limiting value:-

After deciding upon whether to use a Bipolar or MOSFET, the next step in deciding upon a suitable type is by the correct selection of the transistor voltage. For transformer coupled topologies, the maximum voltage developed across the device is normally at turn-off. This will be either half, full or double the magnitude of the input supply voltage, dependent upon the topology used. There may also be a significant voltage spike due to transformer leakage inductance that must be included. The transistor must safely withstand these worst case values without breaking down. Hence, for a bipolar device, a suitably high  $V_{\text{BR(DSS)}}$ . At present 1750V is the maximum blocking voltage available for power Bipolars, and a maximum of 1000V for power MOSFETs.

The selection guides assume that a rectified 220V or 110V mains input is used. The maximum dc link voltages that will be produced for these conditions are 385V and 190V respectively. These values are the input voltage levels used to select the correct device voltage rating.

#### (ii) Current limiting value:-

The Bipolar device has a very low voltage drop across it during conduction, which is relatively constant within the rated current range. Hence, for maximum utilisation of a bipolar transistor, it should be run close to its  $I_{Csat}$  value. This gives a good compromise between cost, drive requirements and switching. The maximum current for a particular throughput power is calculated for each topology

using simple equations. These equations are listed in the appropriate sections, and the levels obtained used to select a suitable Bipolar device.

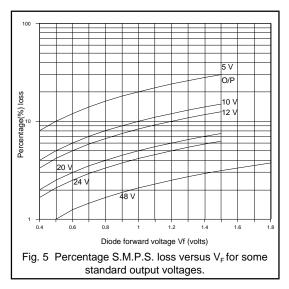

The MOSFET device operates differently from the bipolar in that the voltage developed across it (hence, transistor dissipation) is dependent upon the current flowing and the device "on-resistance" which is variable with temperature. Hence, the optimum MOSFET for a given converter can only be chosen on the basis that the device must not exceed a certain percentage of throughput (output) power. (In this selection a 5% loss in the MOSFET was assumed). A set of equations used to estimate the correct MOSFET  $R_{DS(on)}$ value for a particular power level has been derived for each topology. These equations are included in Appendix A at the end of the paper. The value of RDS(on) obtained was then used to select a suitable MOSFET device for each requirement.

NOTE! This method assumes negligible switching losses in the MOSFET. However for frequencies above 50kHz, switching losses become increasingly significant.

#### **Rectifiers**

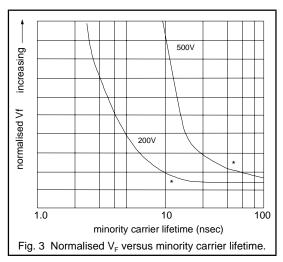

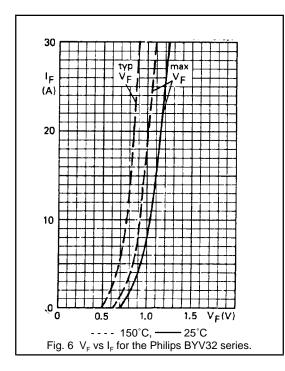

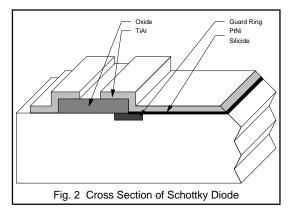

Two types of output rectifier are specified from the Philips range. For very low output voltages below 10V it is necessary to have an extremely low rectifier forward voltage drop, V<sub>F</sub>, in order to keep converter efficiency high. Schottky types are specified here, since they have very low V<sub>F</sub> values (typically 0.5V). The Schottky also has negligible switching losses and can be used at very high frequencies. Unfortunately, the very low V<sub>F</sub> of the Schottky is lost at higher reverse blocking voltages (typically above 100V) and other diode types become more suitable. This means that the Schottky is normally reserved for use on outputs up to 20V or so.

Note. A suitable guideline in selecting the correct rectifier reverse voltage is to ensure the device will block 4 to 6 times the output voltage it is used to provide (depends on topology and whether rugged devices are being used).

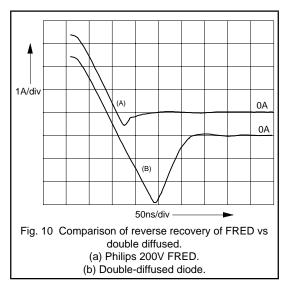

For higher voltage outputs the most suitable rectifier is the fast recovery epitaxial diode (FRED). This device has been optimised for use in high frequency rectification. Its characteristics include low  $V_F$  (approx. 1V) with very fast and efficient switching characteristics. The FRED has reverse voltage blocking capabilities up to 800V. They are therefore suitable for use in outputs from 10 to 200V.

The rectifier devices specified in each selection guide were chosen as having the correct voltage limiting value and high enough current handling capability for the particular output power specified. (A single output is assumed).

## (5) Standard isolated topologies.

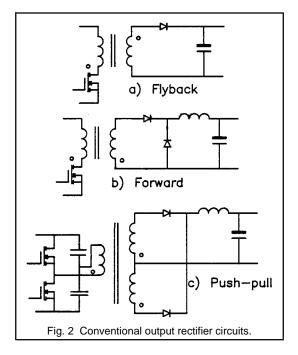

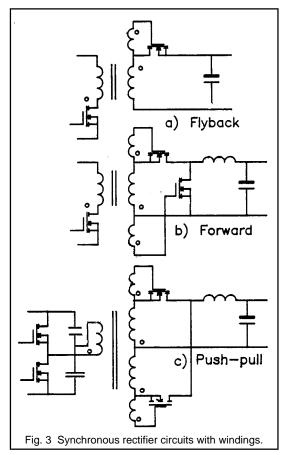

## (a) The Flyback converter.

#### **Operation**

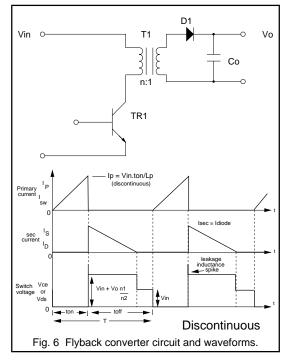

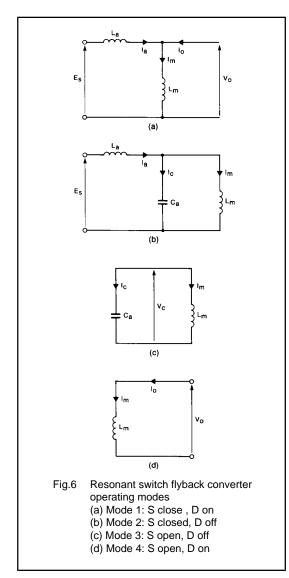

Of all the isolated converters, by far the simplest is the single-ended flyback converter shown in Fig. 6. The use of a single transistor switch means that the transformer can only be driven unipolar (asymmetrical). This results in a large core size. The flyback, which is an isolated version of the buck-boost, does not in truth contain a transformer but a coupled inductor arrangement. When the transistor is turned on, current builds up in the primary and energy is stored in the core, this energy is then released to the output circuit through the secondary when the switch is turned off. (A normal transformer such as the types used in the buck derived topologies couples the energy directly during transistor on-time, ideally storing no energy).

The polarity of the windings is such that the output diode blocks during the transistor on time. When the transistor turns off, the secondary voltage reverses, maintaining a constant flux in the core and forcing secondary current to flow through the diode to the output load. The magnitude

of the peak secondary current is the peak primary current reached at transistor turn-off reflected through the turns ratio, thus maintaining a constant Ampere-turn balance.

The fact that all of the output power of the flyback has to be stored in the core as  $1/2Ll^2$  energy means that the core size and cost will be much greater than in the other topologies, where only the core excitation (magnetisation) energy, which is normally small, is stored. This, in addition to the initial poor unipolar core utilisation, means that the transformer bulk is one of the major drawbacks of the flyback converter.

In order to obtain sufficiently high stored energy, the flyback primary inductance has to be significantly lower than required for a true transformer, since high peak currents are needed. This is normally achieved by gapping the core. The gap reduces the inductance, and most of the high peak energy is then stored in the gap, thus avoiding transformer saturation.

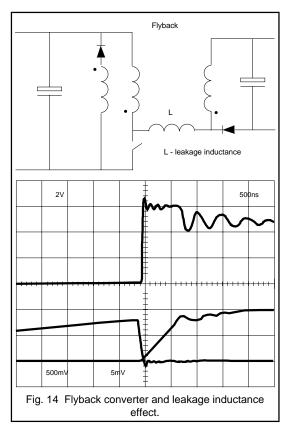

When the transistor turns off, the output voltage is back reflected through the transformer to the primary and in many cases this can be nearly as high as the supply voltage. There is also a voltage spike at turn-off due to the stored energy in the transformer leakage inductance. This means that the transistor must be capable of blocking approximately twice the supply voltage plus the leakage spike. Hence, for a 220V ac application where the dc link can be up to 385V, the transistor voltage limiting value must lie between 800 and 1000V.

Using a 1000V Bipolar transistor such as the BUT11A or BUW13A allows a switching frequency of 30kHz to be used at output powers up to 200Watts.

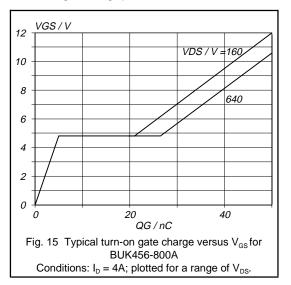

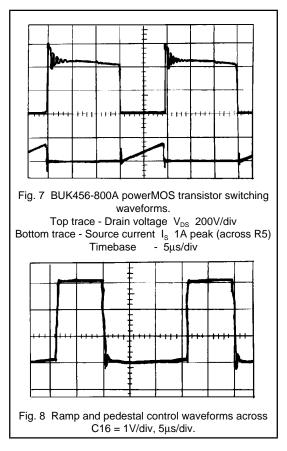

MOSFETs with 800V and 1000V limiting values can also be used, such as the BUK456-800A which can supply 100W at switching frequencies anywhere up to 300kHz. Although the MOSFET can be switched much faster and has lower switching losses, it does suffer from significant on-state losses, especially in the higher voltage devices when compared to the bipolars. An outline of suitable transistors and output rectifiers for different input and power levels using the flyback is given in Table 2.

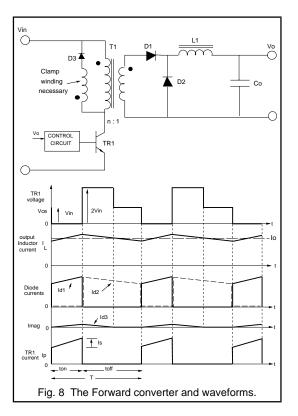

One way of removing the transformer leakage voltage spike is to add a clamp winding as shown in Fig. 8. This allows the leakage energy to be returned to the input instead of stressing the transistor. The diode is always placed at the high voltage end so that the clamp winding capacitance does not interfere with the transistor turn-on current spike, which would happen if the diode was connected to ground. This clamp is optional and depends on the designer's particular requirements.

#### Advantages.

The action of the flyback means that the secondary inductance is in series with the output diode when current is delivered to the load; i.e driven from a current source. This means that no filter inductor is needed in the output circuit. Hence, each output requires only one diode and output filter capacitor. This means the flyback is the ideal choice for generating low cost, multiple output supplies. The cross regulation obtained using multiple outputs is also very good (load changes on one output have little effect on the others) because of the absence of the output choke, which degrades this dynamic performance.

The flyback is also ideally suited for generating high voltage outputs. If a buck type LC filter was used to generate a high voltage, a very large inductance value would be needed to reduce the ripple current levels sufficiently to achieve the continuous mode operation required. This restriction does not apply to the flyback, since it does not require an output inductance for successful operation.

#### Disadvantages.

From the flyback waveforms in Fig. 6 it is clear that the output capacitor is only supplied during the transistor off time. This means that the capacitor has to smooth a pulsating output current which has higher peak values than the continuous output current that would be produced in a forward converter, for example. In order to achieve low output ripple, very large output capacitors are needed, with very low equivalent series resistance (e.s.r). It can be shown that at the same frequency, an LC filter is approximately 8 times more effective at ripple reduction than a capacitor alone. Hence, flybacks have inherently much higher output ripples than other topologies. This, together with the higher peak currents, large capacitors and transformers, limits the flyback to lower output power applications in the 20 to 200W range. (It should be noted that at higher voltages, the required output voltage ripple magnitudes are not normally as stringent, and this means that the e.s.r requirement and hence capacitor size will not be as large as expected.)

#### Two transistor flyback.

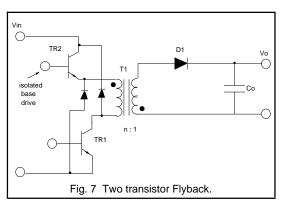

One possible solution to the 1000V transistor requirement is the two transistor flyback version shown in Fig. 7. Both transistors are switched simultaneously, and all waveforms are exactly the same, except that the voltage across each transistor never exceeds the input voltage. The clamp winding is now redundant, since the two clamp diodes act to return leakage energy to the input. Two 400 or 500V devices can now be selected, which will have faster switching and lower conduction losses. The output power and switching frequencies can thus be significantly increased. The drawbacks of the two transistor version are the extra cost and more complex isolated base drive needed for the top floating transistor.

Continuous Vs Discontinuous operation.

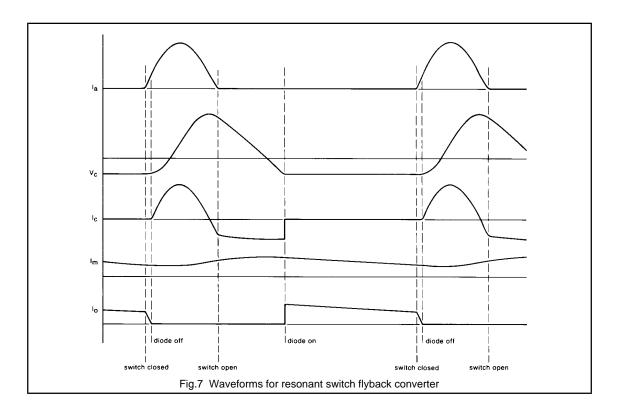

As with the buck-boost, the flyback can operate in both continuous and discontinuous modes. The waveforms in Fig. 6 show discontinuous mode operation. In discontinuous mode, the secondary current falls to zero in each switching period, and all of the energy is removed from the transformer. In continuous mode there is current flowing in the coupled inductor at all times, resulting in trapezoidal current waveforms.

The main plus of continuous mode is that the peak currents flowing are only half that of the discontinuous for the same output power, hence, lower output ripple is possible. However, the core size is about 2 to 4 times larger in continuous mode to achieve the increased inductance needed to reduce the peak currents to achieve continuity.

A further disadvantage of continuous mode is that the closed loop is far more difficult to control than the discontinuous mode flyback. (Continuous mode contains a right hand plane zero in its open loop frequency response, the discontinuous flyback does not. See Ref[2] for further explanation.) This means that much more time and effort is required for continuous mode to design the much more complicated compensation components needed to achieve stability.

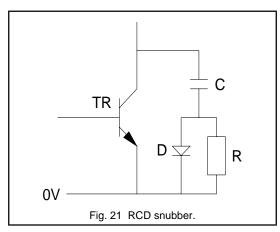

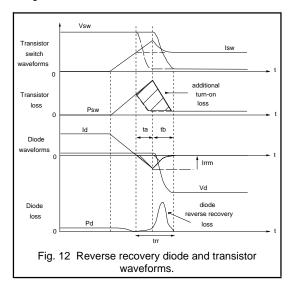

There is negligible turn-on dissipation in the transistor in discontinuous mode, whereas this dissipation can be fairly high in continuous mode, especially when the additional effects of the output diode reverse recovery current, which only occurs in the continuous case, is included. This normally means that a snubber must be added to protect the transistor against switch-on stresses.

One advantage of the continuous mode is that its open loop gain is independent of the output load i.e  $V_o$  only depends upon D and  $V_{in}$  as shown in the dc gain equation at the end of the section. Continuous mode has excellent open loop load regulation, i.e varying the output load will not affect  $V_o$ . Discontinuous mode, on the other-hand, does have a dependency on the output, expressed as  $R_L$  in the dc gain equation. Hence, discontinuous mode has a much poorer

open loop load regulation, i.e changing the output will affect  $V_o$ . This problem disappears, however, when the control loop is closed, and the load regulation problem is usually completely overcome.

The use of current mode control with discontinuous flyback (where both the primary current and output voltage are sensed and combined to control the duty cycle) produces a much improved overall loop regulation, requiring less closed loop gain.

Although the discontinuous mode has the major disadvantage of very high peak currents and a large output capacitor requirement, it is much easier to implement, and is by far the more common of the two methods used in present day designs.

| Output power                                                                     | 50W                                         |                                | 100W                                            |                                | 200W                                                        |                           |

|----------------------------------------------------------------------------------|---------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------------------|---------------------------|

| Line voltage, Vin                                                                | 110V ac                                     | 220V ac                        | 110V ac                                         | 220V ac                        | 110V ac                                                     | 220V ac                   |

| Transistor requirements<br>Max current<br>Max voltage                            | 2.25A<br>400V                               | 1.2A<br>800V                   | 4A<br>400V                                      | 2.5A<br>800V                   | 8A<br>400V                                                  | 4.4A<br>800V              |

| Bipolar transistors.<br>TO-220<br>Isolated SOT-186<br>SOT-93<br>Isolated SOT-199 | BUT11<br>BUT11F<br><br>                     | BUX85<br>BUX85F<br>            | BUT12<br>BUT12F<br>                             | BUT11A<br>BUT11AF<br>          | <br><br>BUW13<br>BUW13F                                     | BUT12A<br>BUT12AF<br><br> |

| Power MOSFET<br>TO-220<br>Isolated SOT-186<br>SOT-93                             | BUK454-400B<br>BUK444-400B<br>              | BUK454-800A<br>BUK444-800A<br> | BUK455-400B<br>BUK445-400B<br>                  | BUK456-800A<br>BUK446-800A<br> | <br><br>BUK437-400B                                         | <br><br>BUK438-800A       |

| Output Rectifiers<br>O/P voltage<br>5V<br>10V                                    | PBYR1635<br>PBYR10100<br>BYW29E-100/150/200 |                                | PBYR2535CT<br>PBYR20100CT<br>BYV79E-100/150/200 |                                | <br>PBYR30100PT<br>BYV42E-100/150/200<br>BYV72E-100/150/200 |                           |

| 20V                                                                              | PBYR10100<br>BYW29E-100/150/200             |                                | PBYR10100<br>BYW29E-100/150/200                 |                                | PBYR20100CT<br>BYV32E-100/150/200                           |                           |

| 50V<br>100V                                                                      | BYV2<br>BYV2                                |                                | BYV29-300<br>BYV29-500                          |                                | BYV29-300<br>BYV29-500                                      |                           |

Table 2. Recommended Power Semiconductors for single-ended flyback.

Note! The above values are for discontinuous mode. In continuous mode the peak transistor currents are approximately halved and the output power available is thus increased.

$$\frac{Flyback}{Converter efficiency, \eta = 80\%; Max duty cycle, D_{max} = 0.45}$$

Max transistor voltage, V<sub>ce</sub> or V<sub>ds</sub> = 2V<sub>in(max</sub>) + leakage spike

$$Max transistor current, I_c \quad ; \quad I_D = 2 \frac{P_{out}}{\eta \quad D_{max} \quad V_{min}}$$

dc voltage gain:- (a) continuous  $\frac{Vo}{Vin} = n \frac{D}{1-D}$

(b) Discontinuous  $\frac{Vo}{Vin} = D \sqrt{\frac{R_L \quad T}{2 \quad L_p}}$

Applications:- Lowest cost, multiple output supplies in the 20 to 200W range. E.g. mains input T.V. supplies, small computer supplies, E.H.T. supplies.

## (b) The Forward converter.

#### Operation.

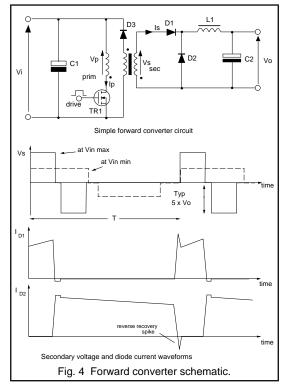

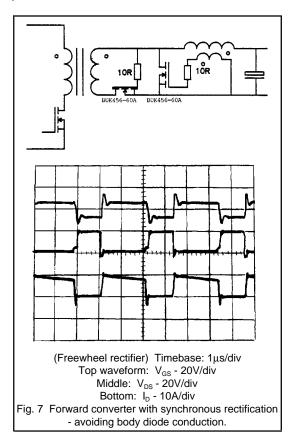

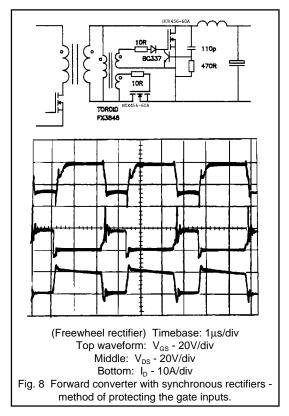

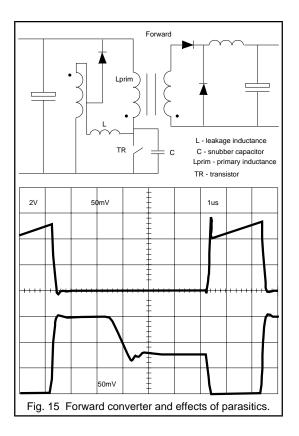

The forward converter is also a single switch isolated topology, and is shown in Fig. 8. This is based on the buck converter described earlier, with the addition of a transformer and another diode in the output circuit. The characteristic LC output filter is clearly present.

In contrast to the flyback, the forward converter has a true transformer action, where energy is transferred directly to the output through the inductor during the transistor on-time. It can be seen that the polarity of the secondary winding is opposite to that of the flyback, hence allowing direct current flow through blocking diode D1. During the on-time, the current flowing causes energy to be built up in the output inductor L1. When the transistor turns off, the secondary voltage reverses, D1 goes from conducting to blocking mode and the freewheel diode D2 then becomes forward biased and provides a path for the inductor current to continue to flow. This allows the energy stored in L1 to be released into the load during the transistor off time.

The forward converter is always operated in continuous mode (in this case the output inductor current), since this produces very low peak input and output currents and small ripple components. Going into discontinuous mode would greatly increase these values, as well as increasing the amount of switching noise generated. No destabilising right hand plane zero occurs in the frequency response of the forward in continuous mode (as with the buck). See Ref[2]. This means that the control problems that existed with the continuous flyback are not present here. So there are no real advantages to be gained by using discontinuous mode operation for the forward converter.

#### Advantages.

As can be seen from the waveforms in Fig. 8, the inductor current  $I_L$ , which is also the output current, is always continuous. The magnitude of the ripple component, and hence the peak secondary current, depends upon the size of the output inductor. Therefore, the ripple can be made relatively small compared to the output current, with the peak current minimised. This low ripple, continuous output current is very easy to smooth, and so the requirements for the output capacitor size, e.s.r and peak current handling are far smaller than they are for the flyback.

Since the transformer in this topology transfers energy directly there is negligible stored energy in the core compared to the flyback. However, there is a small magnetisation energy required to excite the core, allowing it to become an energy transfer medium. This energy is very small and only a very small primary magnetisation current is needed. This means that a high primary inductance is usually suitable, with no need for the core air gap required in the flyback. Standard un-gapped ferrite cores with high permeabilities (2000-3000) are ideal for providing the high inductance required. Negligible energy storage means that the forward converter transformer is considerably smaller than the flyback, and core loss is also much smaller for the same throughput power. However, the transformer is still operated asymmetrically, which means that power is only transferred during the switch on-time, and this poor utilisation means the transformer is still far bigger than in the symmetrical types.

The transistors have the same voltage rating as the discontinuous flyback (see disadvantages), but the peak current required for the same output power is halved, and this can be seen in the equations given for the forward converter. This, coupled with the smaller transformer and output filter capacitor requirements means that the forward converter is suitable for use at higher output powers than the flyback can attain, and is normally designed to operate in the 100 to 400W range. Suitable bipolars and MOSFETs for the forward converter are listed in Table 3.

#### Disadvantages.

Because of the unipolar switching action of the forward converter, there is a major problem in how to remove the core magnetisation energy by the end of each switching cycle. If this did not happen, there would be a net dc flux build-up, leading to core saturation, and possible transistor destruction. This magnetisation energy is removed automatically by the push-pull action of the symmetrical types. In the flyback this energy is dumped into the load at transistor turn-off. However, there is no such path in the forward circuit.

This path is provided by adding an additional reset winding of opposite polarity to the primary. A clamp diode is added, such that the magnetisation energy is returned to the input supply during the transistor off time. The reset winding is wound bifilar with the primary to ensure good coupling, and is normally made to have the same number of turns as the primary. (The reset winding wire gauge can be very small, since it only has to conduct the small magnetisation current.) The time for the magnetisation energy to fall to zero is thus the same duration as the transistor on-time. This means that the maximum theoretical duty ratio of the forward converter is 0.5 and after taking into account switching delays, this falls to 0.45. This limited control range is one of the drawbacks of using the forward converter. The waveform of the magnetisation current is also shown in Fig. 8. The clamp winding in the flyback is optional, but is always needed in the forward for correct operation.

Due to the presence of the reset winding, in order to maintain volt-sec balance within the transformer, the input voltage is back reflected to the primary from the clamp winding at transistor turn-off for the duration of the flow of the magnetisation reset current through D3. (There is also a voltage reversal across the secondary winding, and this is why diode D1 is added to block this voltage from the output circuit.) This means that the transistor must block two times Vin during switch-off. The voltage returns to Vin after reset has finished, which means transistor turn-on losses will be smaller. The transistors must have the same added burden of the voltage rating of the flyback, i.e 400V for 110V mains and 800V for 220V mains applications.

#### Output diode selection.

The diodes in the output circuit both have to conduct the full magnitude of the output current. They are also subject to abrupt changes in current, causing a reverse recovery spike, particularly in the freewheel diode, D2. This spike can cause additional turn-on switching loss in the transistor, possibly causing device failure in the absence of snubbing. Thus, very high efficiency, fast trr diodes are required to minimise conduction losses and to reduce the reverse recovery spike. These requirements are met with Schottky diodes for outputs up to 20V, and fast recovery epitaxial diodes for higher voltage outputs. It is not normal for forward converter outputs to exceed 100V because of the need for

a very large output choke, and flybacks are normally used. Usually, both rectifiers are included in a single package i.e a dual centre-tap arrangement. The Philips range of Schottkies and FREDs which meet these requirements are also included in Table 3.

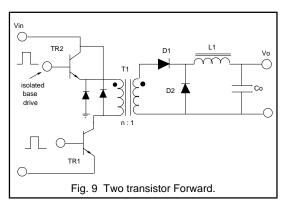

#### Two transistor forward.

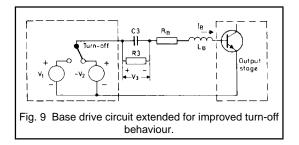

In order to avoid the use of higher voltage transistors, the two transistor version of the forward can be used. This circuit, shown in Fig. 9, is very similar to the two transistor flyback and has the same advantages. The voltage across the transistor is again clamped to  $V_{in}$ , allowing the use of faster more efficient 400 or 500V devices for 220V mains applications. The magnetisation reset is achieved through the two clamp diodes, permitting the removal of the clamp winding.

The two transistor version is popular for off-line applications. It provides higher output powers and faster switching frequencies. The disadvantages are again the extra cost of the higher component count, and the need for an isolated drive for the top transistor.

Although this converter has some drawbacks, and utilises the transformer poorly, it is a very popular selection for the power range mentioned above, and offers simple drive for the single switch and cheap component costs. Multiple output types are very common. The output inductors are normally wound on a single core, which has the effect of improving dynamic cross regulation, and if designed correctly also reduces the output ripple magnitudes even further. The major advantage of the forward converter is the very low output ripple that can be achieved for relatively small sized LC components. This means that forward converters are normally used to generate lower voltage, high current multiple outputs such as 5, 12, 15, 28V from off-line where lower mains applications. ripple specifications are normally specified for the outputs. The high peak currents that would occur if a flyback was used would place an impossible burden on the smoothing capacitor.

| Output power                                                                     | 10                                              | 100W                           |                                                            | 200W                           |                                       | 300W                      |  |

|----------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------|------------------------------------------------------------|--------------------------------|---------------------------------------|---------------------------|--|

| Line voltage, Vin                                                                | 110V ac                                         | 220V ac                        | 110V ac                                                    | 220V ac                        | 110V ac                               | 220V ac                   |  |

| Transistor requirements<br>Max current<br>Max voltage                            | 2.25A<br>400V                                   | 1.2A<br>800V                   | 4A<br>400V                                                 | 2.5A<br>800V                   | 6A<br>400V                            | 3.3A<br>800V              |  |

| Bipolar transistors.<br>TO-220<br>Isolated SOT-186<br>SOT-93<br>Isolated SOT-199 | BUT11<br>BUT11F<br>                             | BUX85<br>BUX85F<br>            | BUT12<br>BUT12F<br>                                        | BUT11A<br>BUT11AF<br>          | <br><br>BUW13<br>BUW13F               | BUT12A<br>BUT12AF<br><br> |  |

| Power MOSFET<br>TO-220<br>Isolated SOT-186<br>SOT-93                             | BUK454-400B<br>BUK444-400B<br>                  | BUK454-800A<br>BUK444-800A<br> | BUK455-400B<br>BUK445-400B<br>                             | BUK456-800A<br>BUK446-800A<br> | <br><br>BUK437-400B                   | <br><br>BUK438-800A       |  |

| Output Rectifiers (dual)<br>O/P voltage<br>5V<br>10V                             | PBYR2535CT<br>PBYR20100CT<br>BYV32E-100/150/200 |                                | <br>PBYR30100PT<br>BYV42E-100/150/200<br>BYV72E100/150/200 |                                | <br>PBYR30100PT<br>BYV72E-100/150/200 |                           |  |

| 20V                                                                              | PBYR20100CT<br>BYQ28E-100/150/200               |                                | PBYR20100CT<br>BYV32E-100/150/200                          |                                | PBYR20100CT<br>BYV32E-100/150/200     |                           |  |

| 50V                                                                              | BYT2                                            | 8-300                          | BYT28-300                                                  |                                | BYT28-300                             |                           |  |

Table 3. Recommended Power Semiconductors for single-ended forward.

Forward

Converter efficiency,  $\eta = 80\%$ ; Max duty cycle,  $D_{max} = 0.45$

Max transistor voltage,  $V_{ce}$  or  $V_{ds} = 2V_{in(max)}$

Max transistor current,  $I_C$ ;  $I_D = \frac{P_{out}}{\eta - D_{max} - V_{min}}$

dc voltage gain:-  $\frac{Vo}{Vin} = n - D$

Applications:-</u> Low cost, low output ripple, multiple output supplies in the 50 to 400W range. E.g. small computer

supplies, DC/DC converters.

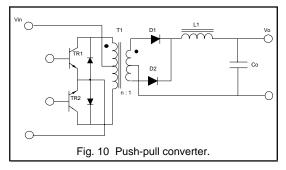

## (c) The Push-pull converter.

Operation.

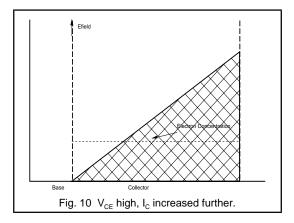

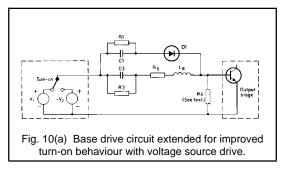

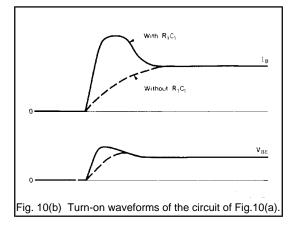

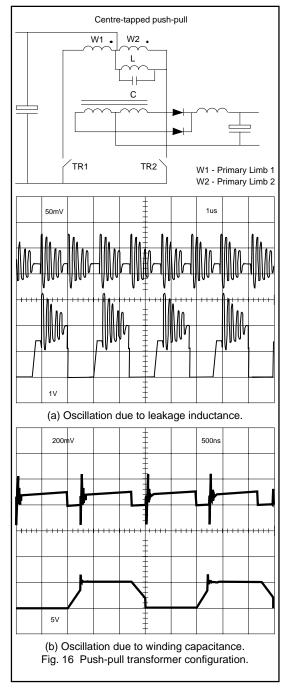

To utilise the transformer flux swing fully, it is necessary to operate the core symmetrically as described earlier. This permits much smaller transformer sizes and provides higher output powers than possible with the single ended types. The symmetrical types always require an even number of transistor switches. One of the best known of the symmetrical types is the push-pull converter shown in Fig. 10.

The primary is a centre-tapped arrangement and each transistor switch is driven alternately, driving the transformer in both directions. The push-pull transformer is typically half the size of that for the single ended types, resulting in a more compact design. This push-pull action produces natural core resetting during each half cycle, hence no clamp winding is required. Power is transferred to the buck type output circuit during each transistor conduction period. The duty ratio of each switch is usually less than 0.45. This provides enough dead time to avoid transistor cross conduction. The power can now be transferred to the output for up to 90% of the switching period, hence allowing greater throughput power than with the single-ended types. The push-pull configuration is normally used for output powers in the 100 to 500W range.

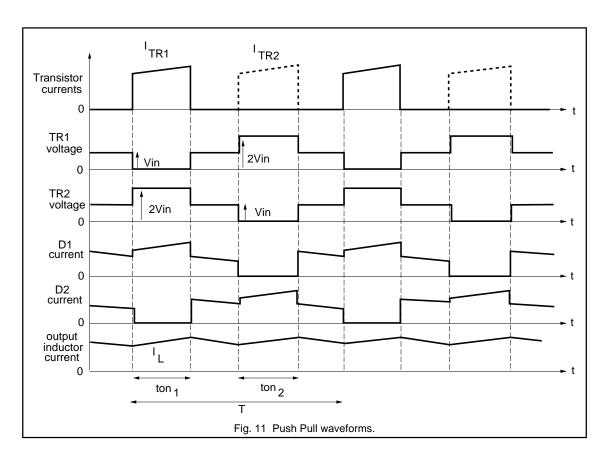

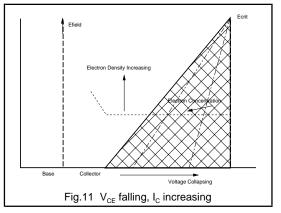

The bipolar switching action also means that the output circuit is actually operated at twice the switching frequency of the power transistors, as can be seen from the waveforms in Fig. 11. Therefore, the output inductor and capacitor can be even smaller for similar output ripple levels. Push-pull converters are thus excellent for high power density, low ripple outputs.

#### Advantages.

As stated, the push-pull offers very compact design of the transformer and output filter, while producing very low output ripple. So if space is a premium issue, the push-pull could be suitable. The control of the push-pull is similar to the forward, in that it is again based on the continuous mode

buck. When closing the feedback control loop, compensation is relatively easy. For multiple outputs, the same recommendations given for the forward converter apply.

Clamp diodes are fitted across the transistors, as shown. This allows leakage and magnetisation energy to be simply channelled back to the supply, reducing stress on the switches and slightly improving efficiency.

The emitter or source of the power transistors are both at the same potential in the push-pull configuration, and are normally referenced to ground. This means that simple base drive can be used for both, and no costly isolating drive transformer is required. (This is not so for the bridge types which are discussed latter.)

#### Disadvantages.

One of the main drawbacks of the push-pull converter is the fact that each transistor must block twice the input voltage due to the doubling effect of the centre-tapped primary, even though two transistors are used. This occurs when one transistor is off and the other is conducting. When both are off, each then blocks the supply voltage, this is shown in the waveforms in Fig. 11. This means that TWO expensive, less efficient 800 to 1000V transistors would be required for a 220V off-line application. A selection of transistors and rectifiers suitable for the push-pull used in off-line applications is given in Table 4.

A further major problem with the push-pull is that it is prone to flux symmetry imbalance. If the flux swing in each half cycle is not exactly symmetrical, the volt-sec will not balance and this will result in transformer saturation, particularly for high input voltages. Symmetry imbalance can be caused by different characteristics in the two transistors such as storage time in a bipolar and different on-state losses.

The centre-tap arrangement also means that extra copper is needed for the primary, and very good coupling between the two halves is necessary to minimise possible leakage spikes. It should also be noted that if snubbers are used to protect the transistors, the design must be very precise since each tends to interact with the other. This is true for all symmetrically driven converters.

These disadvantages usually dictate that the push-pull is normally operated at lower voltage inputs such as 12, 28 or 48V. DC-DC converters found in the automotive and telecommunication industries are often push-pull designs. At these voltage levels, transformer saturation is easier to avoid.

Since the push-pull is commonly operated with low dc voltages, a selection guide for suitable power MOSFETs is also included for 48 and 96V applications, seen in Table 5.

#### Current mode control.

The introduction of current mode control circuits has also benefited the push-pull type. In this type of control, the primary current is monitored, and any imbalance which occurs is corrected on a cycle by cycle basis by varying the duty cycle immediately. Current mode control completely removes the symmetry imbalance problem, and the possibilities of saturation are minimised. This has meant that push-pull designs have become more popular in recent years, with some designers even using them in off-line applications.

| Output power                                                                     | 100                                                                                  | 100W                           |                                | 300W                           |                                 | 500W                      |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|---------------------------------|---------------------------|--|

| Line voltage, Vin                                                                | 110V ac                                                                              | 220V ac                        | 110V ac                        | 220V ac                        | 110V ac                         | 220V ac                   |  |

| Transistor requirements<br>Max current<br>Max voltage                            | 1.2A<br>400V                                                                         | 0.6A<br>800V                   | 4.8A<br>400V                   | 3.0A<br>800V                   | 5.8A<br>400V                    | 3.1A<br>800V              |  |

| Bipolar transistors.<br>TO-220<br>Isolated SOT-186<br>SOT-93<br>Isolated SOT-199 | BUT11<br>BUT11F<br><br>                                                              | BUX85<br>BUX85F<br><br>        | BUT12<br>BUT12F<br><br>        | BUT11A<br>BUT11AF<br>          | <br><br>BUW13<br>BUW13F         | BUT12A<br>BUT12AF<br><br> |  |

| Power MOSFET<br>TO-220<br>Isolated SOT-186<br>SOT-93                             | BUK454-400B<br>BUK444-400B<br>                                                       | BUK454-800A<br>BUK444-800A<br> | BUK455-400B<br>BUK445-400B<br> | BUK456-800A<br>BUK446-800A<br> | <br><br>BUK437-400B             | <br><br>BUK438-800A       |  |

| Output Rectifiers (dual)<br>O/P voltage<br>5V<br>10V<br>20V                      | PBYR2535CT<br>PBYR20100CT<br>BYV32E-100/150/200<br>PBYR20100CT<br>BYQ28E-100/150/200 |                                | PBYR2                          |                                | PBYR3<br>BYV42E-1               |                           |  |

| 50V                                                                              | BYT2                                                                                 | 8-300                          | BYT28-300                      |                                | BYV72E-100/150/200<br>BYV34-300 |                           |  |

Table 4. Recommended Power Semiconductors for off-line Push-pull converter.

| Output power                                         | 100W                           |                                | 200W                           |                                | 300W                |        |

|------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|---------------------|--------|

| Line voltage, Vin                                    | 96V dc                         | 48V dc                         | 96V dc                         | 48V dc                         | 96V dc              | 48V dc |

| Power MOSFET<br>TO-220<br>Isolated SOT-186<br>SOT-93 | BUK455-400B<br>BUK445-400B<br> | BUK454-200A<br>BUK444-200A<br> | BUK457-400B<br>BUK437-400B<br> | BUK456-200B<br>BUK436-200B<br> | <br><br>BUK437-400B |        |

Table 5. Recommended power MOSFETs for lower input voltage push-pull.

$$\begin{array}{l} \underline{Push-Pull\ converter.}\\ Converter\ efficiency,\ \eta=80\%;\ Max\ duty\ cycle,\ D_{max}=0.9\\ Max\ transistor\ voltage,\ V_{ce}\ or\ V_{ds}=2V_{in(max)}+leakage\ spike.\\ Max\ transistor\ current,\ I_{C}\ ;\ I_{D}=\frac{P_{out}}{\eta\ D_{max}\ V_{min}}\\ dc\ voltage\ gain:-\ \frac{Vo}{Vin}=2\ n\ D\\ \hline \\ \underline{Applications:-}\ Compact\ design,\ very\ low\ output\ ripple\ supplies\ in\ the\ 100\ to\ 500W\ range.\ More\ suited\ to\ low\ input\ applications\ E.g.\ battery,\ 28,\ 40V\ inputs,\ high\ current\ outputs.\ Telecommunication\ supplies.\\ \end{array}$$

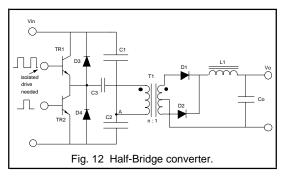

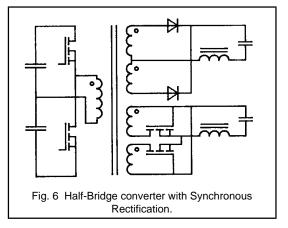

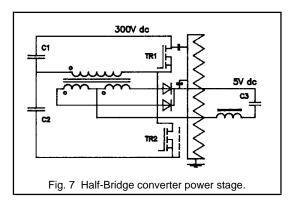

## (d) The Half-Bridge.

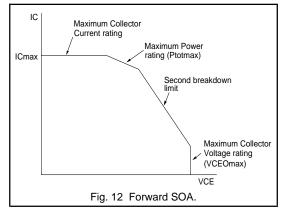

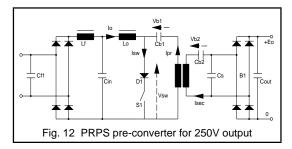

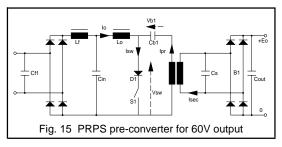

Of all the symmetrical high power converters, the half-bridge converter shown in Fig. 12 is the most popular. It is also referred to as the single ended push-pull, and in principle is a balanced version of the forward converter. Again it is a derivative of the buck. The Half-Bridge has some key advantages over the push-pull, which usually makes it first choice for higher power applications in the 500 to 1000W range.

#### Operation.

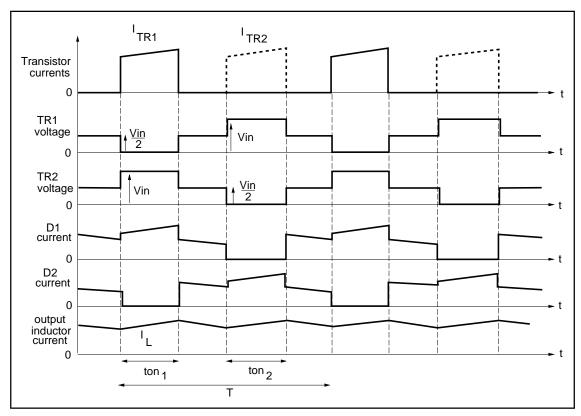

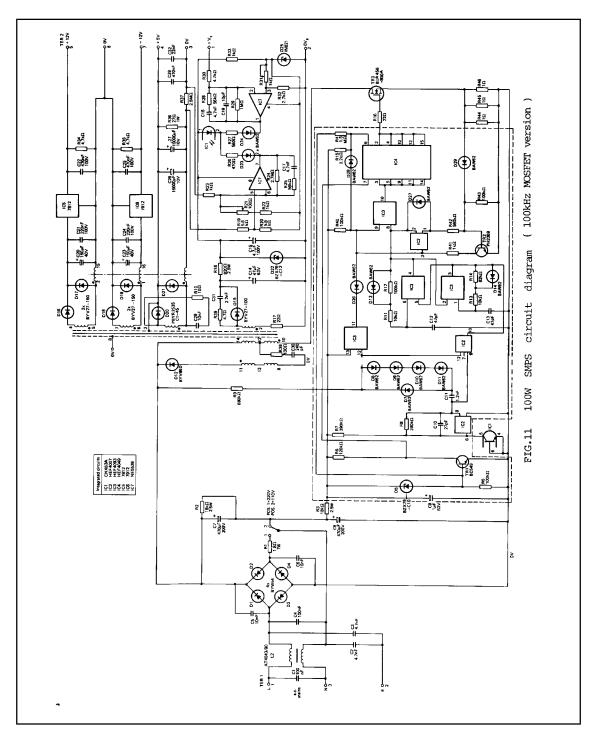

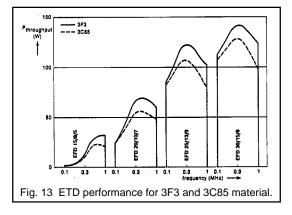

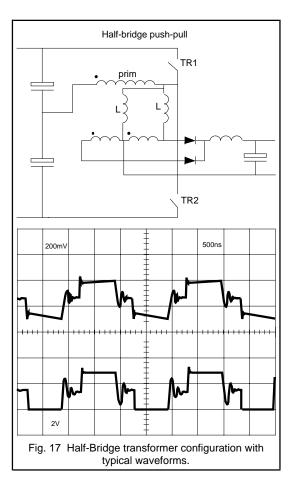

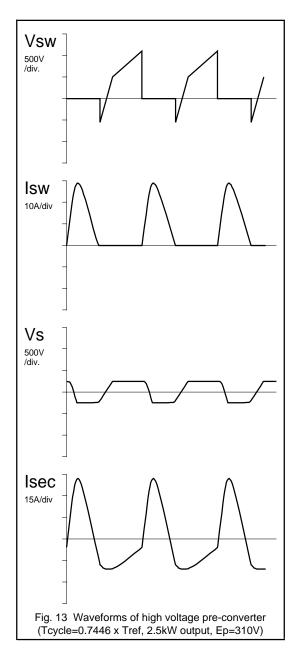

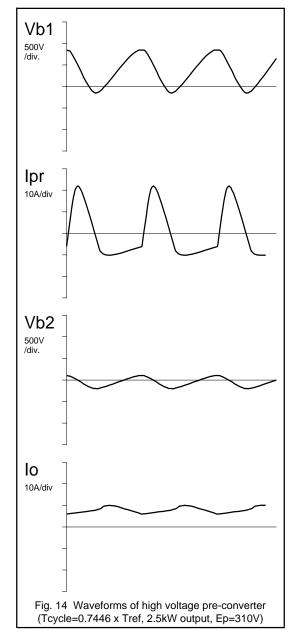

The two mains bulk capacitors C1 and C2 are connected in series, and an artificial input voltage mid-point is provided, shown as point A in the diagram. The two transistor switches are driven alternately, and this connects each capacitor across the single primary winding each half cycle. Vin/2 is superimposed symmetrically across the primary in a push-pull manner. Power is transferred directly to the output on each transistor conduction time and a maximum duty cycle of 90% is available (Some dead time is required to prevent transistor cross-conduction.) Since the primary is driven in both directions, (natural reset) a full wave buck output filter (operating at twice the switching frequency) rather than a half wave filter is implemented. This again results in very efficient core utilisation. As can be seen in Fig. 13, the waveforms are identical to the push-pull, except that the voltage across the transistors is halved. (The device current would be higher for the same output power.)

#### Advantages.

Since both transistors are effectively in series, they never see greater than the supply voltage,  $V_{in}$ . When both are off, their voltages reach an equilibrium point of  $V_{in}/2$ . This is half the voltage rating of the push-pull (although double the

current). This means that the half-bridge is particularly suited to high voltage inputs, such as off-line applications. For example, a 220V mains application can use two higher speed, higher efficiency 450V transistors instead of the 800V types needed for a push-pull. This allows higher frequency operation.

Another major advantage over the push-pull is that the transformer saturation problems due to flux symmetry imbalance are not a problem. By using a small capacitor (less than  $10\mu$ F) any dc build-up of flux in the transformer is blocked, and only symmetrical ac is drawn from the input.

The configuration of the half-bridge allows clamp diodes to be added across the transistors, shown as D3 and D4 in Fig. 12. The leakage inductance and magnetisation energies are dumped straight back into the two input capacitors, protecting the transistors from dangerous transients and improving overall efficiency.

A less obvious exclusive advantage of the half-bridge is that the two series reservoir capacitors already exist, and this makes it ideal for implementing a voltage doubling circuit. This permits the use of either 110V /220V mains as selectable inputs to the supply.

The bridge circuits also have the same advantages over the single-ended types that the push-pull possesses, including excellent transformer utilisation, very low output ripple, and high output power capabilities. The limiting factor in the maximum output power available from the half-bridge is the peak current handling capabilities of present day transistors. 1000W is typically the upper power limit. For higher output powers the four switch full bridge is normally used.

#### Disadvantages.

The need for two 50/60 Hz input capacitors is a drawback because of their large size. The top transistor must also have isolated drive, since the gate / base is at a floating potential. Furthermore, if snubbers are used across the power transistors, great care must be taken in their design, since the symmetrical action means that they will interact with one another. The circuit cost and complexity have clearly increased, and this must be weighed up against the advantages gained. In many cases, this normally excludes the use of the half-bridge at output power levels below 500W.

Suitable transistors and rectifiers for the half-bridge are given in Table 6.

Fig. 13 Half-Bridge waveforms.

| Output power                                                                     | 300W                                                                       |                         | 500W                                      |                         | 750W          |                         |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|-------------------------------------------|-------------------------|---------------|-------------------------|

| Line voltage, Vin                                                                | 110V ac                                                                    | 220V ac                 | 110V ac                                   | 220V ac                 | 110V ac       | 220V ac                 |

| Transistor requirements<br>Max current<br>Max voltage                            | 4.9A<br>250V                                                               | 2.66A<br>450V           | 11.7A<br>250V                             | 6.25A<br>450V           | 17.5A<br>250V | 9.4A<br>450V            |

| Bipolar transistors.<br>TO-220<br>Isolated SOT-186<br>SOT-93<br>Isolated SOT-199 | BUT12<br>BUT12F<br>                                                        | BUT11<br>BUT11F<br><br> | <br><br>BUW13<br>BUW13F                   | <br><br>BUW13<br>BUW13F | <br><br>      | <br><br>BUW13<br>BUW13F |

| Power MOSFET<br>SOT-93                                                           |                                                                            | BUK437-500B             |                                           |                         |               |                         |

| Output Rectifiers (dual)<br>O/P voltage<br>5V<br>10V<br>20V                      | <br>PBYR30100PT<br>BYV72E-100/150/200<br>PBYR20100CT<br>BYV32E-100/150/200 |                         | <br><br>PBYR30100PT<br>BYV42E-100/150/200 |                         |               |                         |

| 50V                                                                              | BYT2                                                                       | 8-300                   |                                           | 00/150/200<br>4-300     | BYV3          | 4-300                   |

Table 6. Recommended Power Semiconductors for off-line Half-Bridge converter.

Half-Bridge converter.

Converter efficiency,  $\eta = 80\%$ ; Max duty cycle,  $D_{max} = 0.9$

Max transistor voltage,  $V_{ce}$  or  $V_{ds} = V_{in(max)}$  + leakage spike.

Max transistor current,  $I_c$ ;  $I_D = 2 \frac{P_{out}}{\eta \quad D_{max} \quad V_{min}}$

dc voltage gain:-  $\frac{Vo}{Vin} = n$  D

<u>Applications:-</u> High power, up to 1000W. High current, very low output ripple outputs. Well suited for high input voltage applications. E.g. 110, 220, 440V mains. E.g. Large computer supplies, Lab equipment supplies.

## (e) The Full-Bridge.

#### Outline.

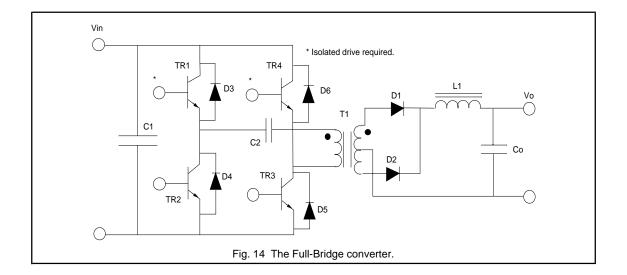

The Full-Bridge converter shown in Fig. 14 is a higher power version of the Half-Bridge, and provides the highest output power level of any of the converters discussed. The maximum current ratings of the power transistors will eventually determine the upper limit of the output power of the half-bridge. These levels can be doubled by using the Full-Bridge, which is obtained by adding another two transistors and clamp diodes to the Half-Bridge arrangement. The transistors are driven alternately in pairs, T1 and T3, then T2 and T4. The transformer primary is now subjected to the full input voltage. The current levels flowing are halved compared to the half-bridge for a given power level. Hence, the Full-Bridge will double the output power of the Half-Bridge using the same transistor types.

The secondary circuit operates in exactly the same manner as the push-pull and half-bridge, also producing very low ripple outputs at very high current levels. Therefore, the waveforms for the Full-Bridge are identical to the Half-Bridge waveforms shown in Fig. 13, except for the voltage across the primary, which is effectively doubled (and switch currents halved). This is expressed in the dc gain and peak current equations, where the factor of two comes in, compared with the Half-Bridge.

#### Advantages.

As stated, the Full-Bridge is ideal for the generation of very high output power levels. The increased circuit complexity normally means that the Full-Bridge is reserved for applications with power output levels of 1kW and above. For such high power requirements, designers often select power Darlingtons, since their superior current ratings and switching characteristics provide additional performance and in many cases a more cost effective design.

The Full-Bridge also has the advantage of only requiring one mains smoothing capacitor compared to two for the Half-Bridge, hence, saving space. Its other major advantages are the same as for the Half-Bridge.

#### Disadvantages.

Four transistors and clamp diodes are needed instead of two for the other symmetrical types. Isolated drive for two floating potential transistors is now required. The Full-Bridge has the most complex and costly design of any of the converters discussed, and should only be used where other types do not meet the requirements. Again, the four transistor snubbers (if required) must be implemented carefully to prevent interactions occurring between them.

Table 7 gives an outline of the Philips power semiconductors suitable for use with the Full-Bridge.

| Output power                                                                     | 500W                                                                              |                         | 1000W                   |                         | 200           | 2000W                   |  |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|---------------|-------------------------|--|

| Line voltage, Vin                                                                | 110V ac                                                                           | 220V ac                 | 110V ac                 | 220V ac                 | 110V ac       | 220V ac                 |  |

| Transistor requirements<br>Max current<br>Max voltage                            | 5.7A<br>250V                                                                      | 3.1A<br>450V            | 11.5A<br>250V           | 6.25A<br>450V           | 23.0A<br>250V | 12.5A<br>450V           |  |

| Bipolar transistors.<br>TO-220<br>Isolated SOT-186<br>SOT-93<br>Isolated SOT-199 | BUT12<br>BUT12F<br><br>                                                           | BUT18<br>BUT18F<br><br> | <br><br>BUW13<br>BUW13F | <br><br>BUW13<br>BUW13F |               | <br><br>BUW13<br>BUW13F |  |

| Power MOSFET<br>SOT-93                                                           |                                                                                   | BUK438-500B             |                         |                         |               |                         |  |

| Output Rectifiers (dual)<br>O/P voltage<br>5V<br>10V<br>20V                      | <br>PBYR30100PT<br>BYV42E-100/150/200<br>BYV72E-100/150/200<br>BYV72E-100/150/200 |                         |                         |                         |               |                         |  |

| 50V                                                                              | BYV34-300                                                                         |                         | BYV4                    | 4-300                   | -             |                         |  |

Table 7. Recommended Power Semiconductors for the Full-Bridge converter.

Full-Bridge converter.

Converter efficiency,

$$\eta = 80\%$$

; Max duty cycle,  $D_{max} = 0.9$

Max transistor voltage,  $V_{ce}$  or  $V_{ds} = V_{in(max)}$  + leakage spike.

Max transistor current,  $I_C$ ;  $I_D = \frac{P_{out}}{\eta \quad D_{max} \quad V_{min}}$

dc voltage gain:-  $\frac{V_o}{Vin} = 2 \quad n \quad D$ Applications:-Very high power, normally above 1000W. Very high current, very low ripple outputs. Well suited for

high input voltage applications. E.g. 110, 220, 440V mains. E.g. Computer Mainframe supplies, Large lab equipment

supplies, Telecomm systems.

## Conclusion.

The 5 most common S.M.P.S. converter topologies, the flyback, forward, push-pull, half-bridge and full-bridge types have been outlined. Each has its own particular operating characteristics and advantages, which makes it suited to particular applications.

The converter topology also defines the voltage and current requirements of the power transistors (either MOSFET or Bipolar). Simple equations and calculations used to outline the requirements of the transistors for each topology have been presented. The selection guide for transistors and rectifiers at the end of each topology section shows some of the Philips devices which are ideal for use in S.M.P.S. applications.

## References.

(1) Philips MOSFET Selection Guide For S.M.P.S. by M.J.Humphreys. Philips Power Semiconductor Applications group, Hazel Grove.

(2) Switch Mode Power Conversion - Basic theory and design by K.Kit.Sum. (Published by Marcel Dekker inc.1984)

## Appendix A.

## MOSFET throughput power calculations.

Assumptions made:-

The power loss (Watts) in the transistor due to on-state losses is 5% of the total throughput (output) power.

Switching losses in the transistor are negligible. N.B. At frequencies significantly higher than 50kHz the switching losses may become important.

The device junction temperature,  $T_j$  is taken to be 125°C. The ratio  $R_{ds(125C')}/R_{ds(25'C)}$  is dependent on the voltage of the MOSFET device. Table A1 gives the ratio for the relevant voltage limiting values.

The value of  $V_{\text{s}(\text{min})}$  for each input value is given in Table A2.

| Device voltage limiting value. | R <sub>ds(125C)</sub><br><br>R <sub>ds(25C)</sub> |

|--------------------------------|---------------------------------------------------|

| 100                            | 1.74                                              |

| 200                            | 1.91                                              |

| 400                            | 1.98                                              |

| 500                            | 2.01                                              |

| 800                            | 2.11                                              |

| 1000                           | 2.15                                              |

Table A1. On resistance ratio.

| Main input<br>voltage | Maximum dc link<br>voltage | Minimum dc<br>link<br>voltage |

|-----------------------|----------------------------|-------------------------------|

| 220 / 240V ac         | 385V                       | 200V                          |

| 110 / 120V ac         | 190V                       | 110V                          |

Table A2. Max and Min dc link voltages for mains inputs.

Using the following equations, for a given device with a known  $R_{\rm ds(125^\circ C)},$  the maximum throughput power in each topology can be calculated.

Where:-

$$\begin{array}{l} \mathsf{P}_{\mathsf{th}(\mathsf{max})} = \mathsf{Maximum throughput power.} \\ \mathsf{D}_{\mathsf{max}} = \mathsf{maximum duty cycle.} \\ \tau = \mathsf{required transistor efficiency} \ (0.05 \pm 0.005) \\ \mathsf{Rds}_{(125^{\circ}\mathrm{C})} = \mathsf{R}_{\mathsf{ds}(25^{\circ}\mathrm{C})} \mathsf{x \ ratio.} \\ \mathsf{V}_{\mathsf{s}(\mathsf{min})} = \mathsf{minimum \ dc \ link \ voltage.} \end{array}$$

#### Forward converter.

$$P_{th(max)} = \frac{\tau \times V_{s(min)}^2 \times D_{max}}{R_{ds(125c)}}$$

$$D_{max} = 0.45$$

#### Flyback Converter.

$$P_{th(max)} = \frac{3 \times \tau \times V_{s(min)}^2 \times D_{max}}{4 \times R_{ds(125c)}}$$

$$D_{max} = 0.45$$

#### Push Pull Converter.

$$P_{th(max)} = \frac{\tau \times V_{s(min)}^2 \times D_{max}}{R_{ds(125c)}}$$

$$D_{max} = 0.9$$

#### Half Bridge Converter.

$$P_{th(\max)} = \frac{\tau \times V_{s(\min)}^2 \times D_{\max}}{4 \times R_{ds(125c)}}$$

$$D_{\max} = 0.9$$

#### Full Bridge Converter.

$$P_{th(max)} = \frac{\tau \times V_{s(min)}^2 \times D_{max}}{2 \times R_{ds(125c)}}$$

$$D_{max} = 0.9$$

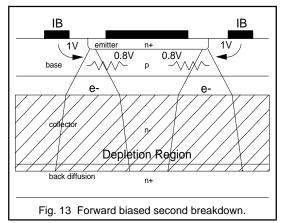

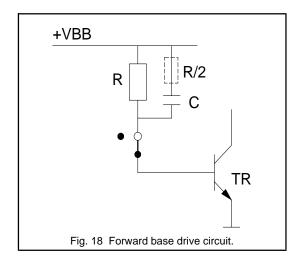

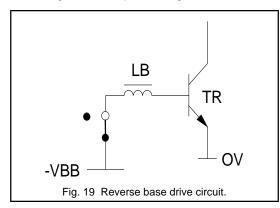

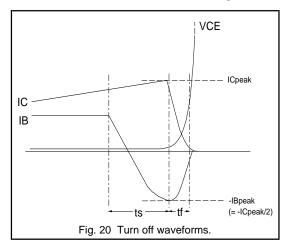

## 2.1.2 The Power Supply Designer's Guide to High Voltage Transistors

One of the most critical components in power switching converters is the high voltage transistor. Despite its wide usage, feedback from power supply designers suggests that there are several features of high voltage transistors which are generally not well understood.

This section begins with a straightforward explanation of the key properties of high voltage transistors. This is done by showing how the basic technology of the transistor leads to its voltage, current, power and second breakdown limits. It is also made clear how deviations from conditions specified in the data book will affect the performance of the transistor. The final section of the paper gives practical advice for designers on how circuits might be optimised and transistor failures avoided.

### Introduction

A large amount of useful information about the characteristics of a given component is provided in the relevant data book. By using this information, a designer can usually be sure of choosing the optimum component for a particular application.

However, if a problem arises with the completed circuit, and a more detailed analysis of the most critical components becomes necessary, the data book can become a source of frustration rather than practical assistance. In the data book, a component is often measured under a very specific set of conditions. Very little is said about how the component performance is affected if these conditions are not reproduced exactly when the component is used in a circuit.

There are as many different sets of requirements for high voltage transistors as there are circuits which make use of them. Covering every possible drive and load condition in the device specification is an impossible task. There is therefore a real need for any designer using high voltage transistors to have an understanding of how deviations from the conditions specified in the transistor data book will affect the electrical performance of the device, in particular its limiting values.

Feedback from designers implies that this information is not readily available. The intention of this report is therefore to provide designers with the information they need in order to optimise the reliability of their circuits. The characteristics of high voltage transistors stem from their basic technology and so it is important to begin with an overview of this.

## **HVT technology**

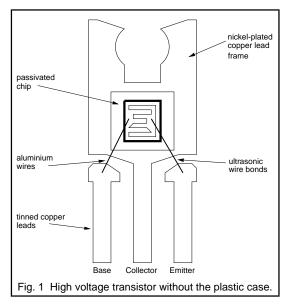

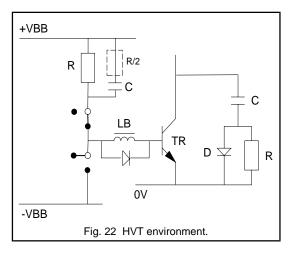

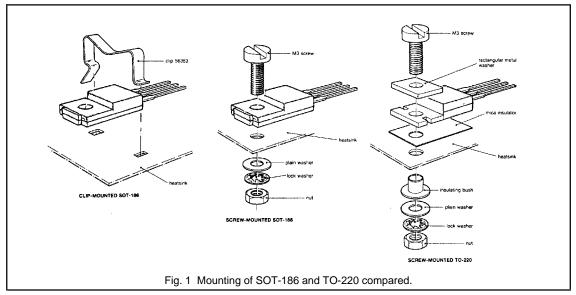

Stripping away the encapsulation of the transistor reveals how the electrical connections are made (see Fig. 1). The collector is contacted through the back surface of the transistor chip, which is soldered to the nickel-plated copper lead frame. For Philips power transistors the lead frame and the centre leg are formed from a single piece of copper, and so the collector can be accessed through either the centre leg or any exposed part of the lead frame (eg the mounting base for TO-220 and SOT-93).

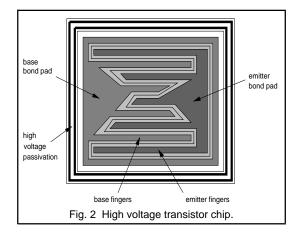

The emitter area of the transistor is contacted from the top surface of the chip. A thin layer of aluminium joins all of the emitter area to a large bond pad. This bond pad is aluminium wire bonded to the emitter leg of the transistor when the transistor is assembled. The same method is used to contact the base area of the chip. Fig. 2 shows the top view of a high voltage transistor chip in more detail.

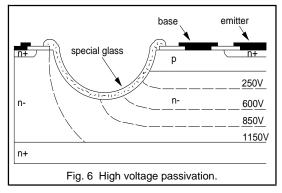

Viewing the top surface of the transistor chip, the base and emitter fingers are clearly visible. Around the periphery of the chip is the high voltage glass passivation. The purpose of this is explained later.

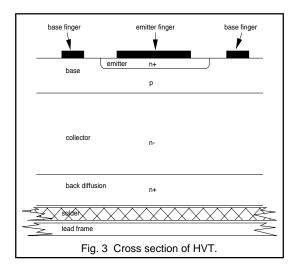

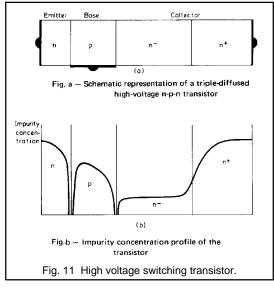

Taking a cross section through the transistor chip reveals its npn structure. A cross section which cuts one of the emitter fingers and two of the base fingers is shown in Fig. 3.

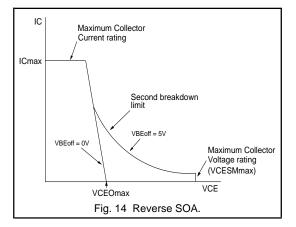

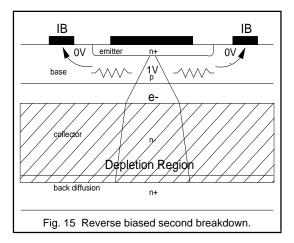

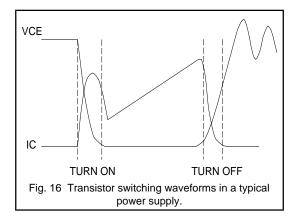

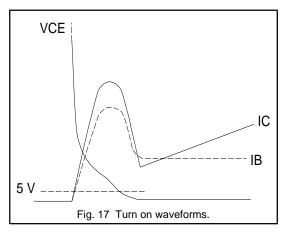

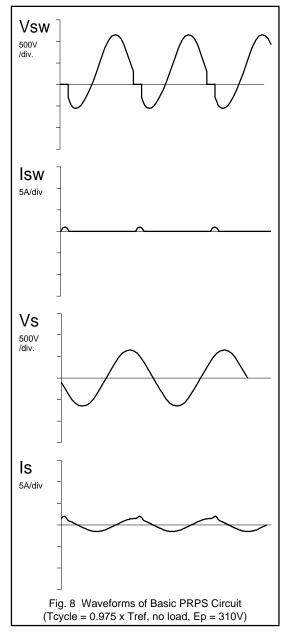

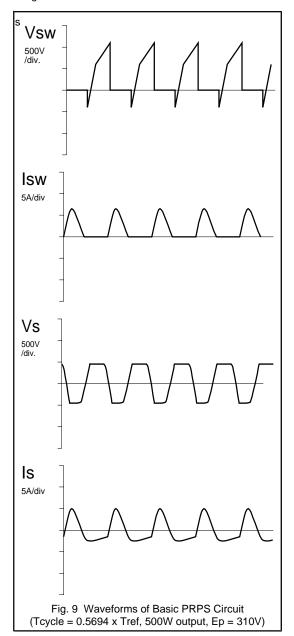

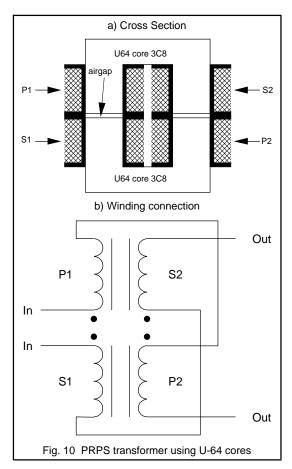

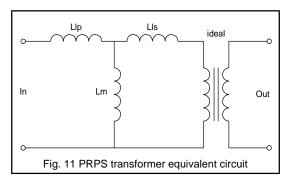

On the top surface of the transistor are the aluminium tracks which contact the base and emitter areas. The emitter finger is shown connected to an n+ region. This is the emitter area. The n+ denotes that this is very highly doped n type silicon. Surrounding the n+ emitter is the base, and as shown in Fig. 3 this is contacted by the base fingers, one on either side of the emitter. The p denotes that this is highly doped p type silicon.