Technical Publication TP105P/R Issue 2 November 1984

# Inverter Grade Stud-Base Thyristor Type P105P/P105R 105 amperes average: up to 800 volts $V_{RRM}/V_{DRM}$

Ratings (Maximum values at 125°C Tj unless stated otherwise)

| RATING                                                 | CONDITIONS                                                                            | SYMBOL             |                                                  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|--------------------------------------------------|

| Average on-state current                               | Half sine wave 85°C case temperature                                                  | l <sub>T(AV)</sub> | 105 A                                            |

| R.M.S. on-state current                                | '                                                                                     | IT (RMS)           | 175 A                                            |

| Continuous on-state current                            |                                                                                       | h                  | 175 A                                            |

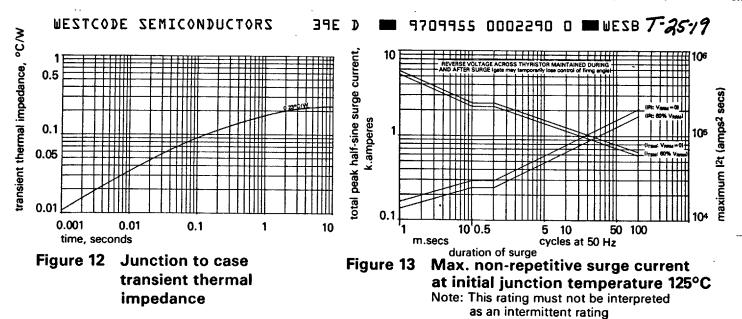

| Peak one-cycle surge (non-repetitive) on state current | 10ms duration, 60% $V_{RRM}$ re-applied 10ms duration, $V_{R} \le 10$ volts           | TSM (1)            | 2200 A<br>2420 A                                 |

| Maximum permissible surge energy                       | 10ms duration, $V_R \le 10 \text{ volts}$<br>3ms duration, $V_R \le 10 \text{ volts}$ | 2t (2)<br> 2t      | 29300 A <sup>2</sup> s<br>22300 A <sup>2</sup> s |

| Peak forward gate current                              | Anode positive with respect to cathode                                                | I <sub>FGM</sub>   | 14 A                                             |

| Peak forward gate voltage                              | Anode positive with respect to cathode                                                | V <sub>EGM</sub>   | 20 V                                             |

| Peak reverse gate voltage                              |                                                                                       | V <sub>RGM</sub>   | 5 V                                              |

| Average gate power                                     |                                                                                       | PG                 | 1.5 W                                            |

| Peak gate power                                        | 100μs. pulse width                                                                    | P <sub>GM</sub>    | 60 W                                             |

| Rate of rise of off-state voltage                      | To 80% V <sub>DRM</sub> gate open-circuit                                             | dv/dt              | *200 V/μs                                        |

| Rate of rise of on-state current (repetitive)          | Gate drive 20 volts, 20 ohms with $t_r \le 1 \mu s$ .                                 | di/dt (1)          | 500 A/μs                                         |

| Rate of rise of on-state current (non-repetitive)      | Anode voltage ≤ 80% V <sub>DRM</sub>                                                  | di/dt (2)          | 1000 A/μs                                        |

| Operating temperature range                            |                                                                                       | T <sub>CASE</sub>  | -40+125°C                                        |

| Storage temperature range                              |                                                                                       | T <sub>stq</sub>   | -40+150°C                                        |

Characteristics (Maximum values at 125°C Tj unless stated otherwise)

| CHARACTERISTIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | CONDITIONS                                                                                                                                         |                                                 |                                                          |     |                                            | SYMBOL                                                                                                                                                                                    |                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Peak on-state voltage Forward conduction threshold voltage Forward conduction slope resistance Repetitive peak off-state current Repetitive peak reverse current Maximum gate current required to fire al Maximum holding current Maximum holding current Maximum gate voltage which will not trig any device Stored charge  Circuit commutated turn-off time available down to Thermal resistance, junction to case for a device with a maximum forward vol drop characteristic | I devices II devices gger | At 280 A,  At V <sub>DRM</sub> At V <sub>RRM</sub> At 25°(  T <sub>M</sub> = 200 A  V <sub>RM</sub> = 50V, 1  T <sub>M</sub> = 200 A  dir/dt = 10A | C, V <sub>A</sub> = 6<br>, dir/dt 1<br>50% chor | V, I <sub>A</sub> = 1A<br>0 A/μs<br>d value<br>= 50V 200 |     | 0% V <sub>DRM</sub><br>0% V <sub>DRM</sub> | V <sub>TM</sub> V <sub>O</sub> r I <sub>DRM</sub> I <sub>RRM</sub> I <sub>GT</sub> V <sub>GT</sub> I <sub>H</sub> V <sub>GD</sub> Q <sub>rr</sub> typical tq typical R <sub>th(j-c)</sub> | 1.71 V<br>1.32 V<br>1.393 mΩ<br>20 mA<br>200 mA<br>200 mA<br>600 mA<br>0.25 V<br>20 μC<br>12-30 μs<br>10-20 μs<br>0.23°C/W |

| VOLTAGE CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           | H02                                                                                                                                                | H04                                             | Н06                                                      | H08 |                                            |                                                                                                                                                                                           |                                                                                                                            |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RRM VDRM<br>VDSM          | 200                                                                                                                                                | 400                                             | 600                                                      | 800 |                                            |                                                                                                                                                                                           |                                                                                                                            |

| Non-repetitive peak reverse blocking volt                                                                                                                                                                                                                                                                                                                                                                                                                                        | age V <sub>RSA</sub>      | 300                                                                                                                                                | 500                                             | 700                                                      | 900 |                                            |                                                                                                                                                                                           |                                                                                                                            |

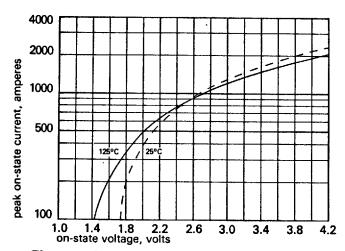

Ordering Information (Please quote device code as explained below)

| Р | 1 0 5 ●                                | • • •                         | •                                                                                 | •                                                                         | 0 |

|---|----------------------------------------|-------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------|---|

|   | P = leaded device<br>R = lugged device | Voltage Code<br>(see ratings) | dv/dt code to 80% V <sub>DRM</sub> C = 20V/µs E = 100V/µs  D = 50V/µs F = 200V/µs | Turn-off time H = 30 μs J = 25 μs K = 20 μs L = 15 μs M = 12 μs N = 10 μs |   |

Typical code: P105PH06FJ0 = 600  $V_{RRM}$  600  $V_{DRM}$  200  $V/\mu s$  dv/dt to 80%  $V_{DRM}$  25  $\mu s$  turn-off

\*Other values of dv/dt up to 1000 V/ $\mu$ s, and turn-off time may be available.

# INTRODUCTION 1.

The P105P thyristor series are diffused regenerative gate devices employing a 19 mm slice in a stud based top-hat housing.

### 2. NOTES ON THE RATINGS

### (a) Rate of rise of on-state current

The maximum un-primed rate of rise of on-state current must not exceed 1000 A/us at any time during turn-on on a non-repetitive basis. For repetitive performance the on-state rate of rise of current must not exceed 500 A/µs at any time during turn-on. Note that these values of current rate of rise apply to the circuit external to the device and its specified snubber network and device current rates of rise will be higher.

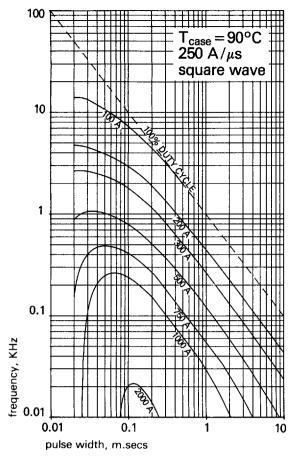

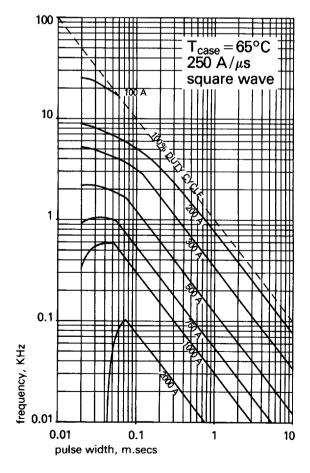

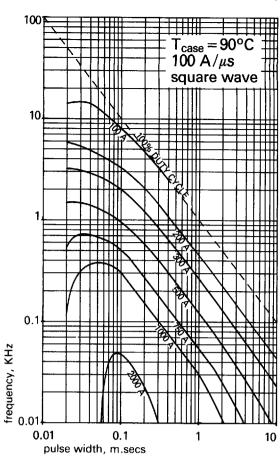

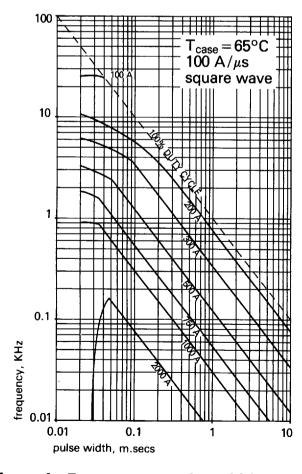

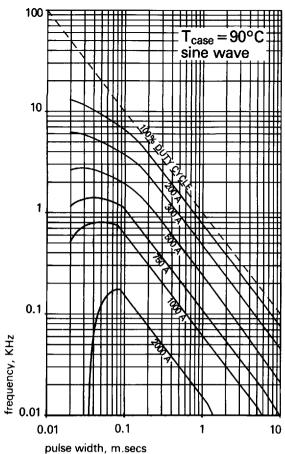

# Square wave ratings

These ratings are given for leading edge linear rates of rise of forward current of 100 and 250 A/us.

# (c)

**Duty Cycle Lines**The 100% duty cycle line appears on all these ratings. These frequency ratings are presented in the form that all duty cycles may be represented by straight parallel lines.

### **Maximum operating Frequency** (d)

The maximum operating frequency, f<sub>max</sub>, is set by the time required for the thyristor to turn off (tg) and for the off-state voltage to reach full value (tv), i.e.

$$f_{\text{max}} = \frac{1}{t_{\text{pulse}} + tq + tv}$$

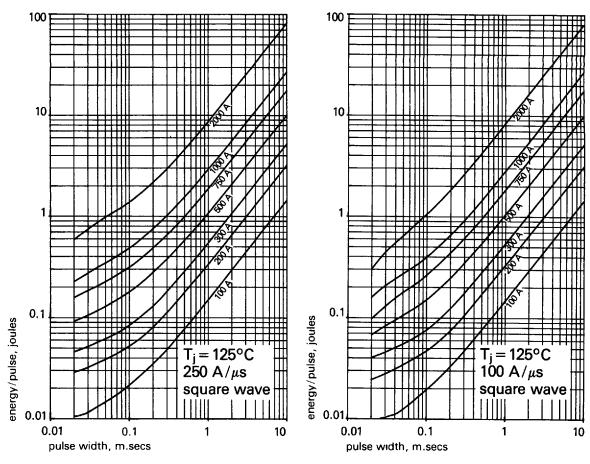

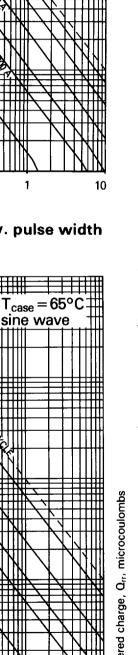

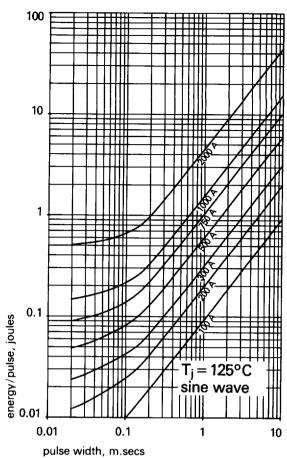

# (e) **Energy per pulse characteristics**

These curves enable rapid estimation of device dissipation to be obtained for conditions not covered by the frequency ratings.

Let Ep be the Energy per pulse for a given current and pulse width, in joules.

Then  $W_{AV} = E_p \times f$ .

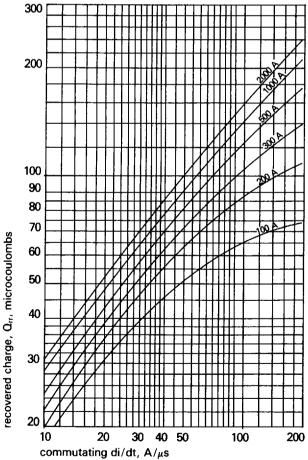

## **REVERSE RECOVERY LOSS** 3.

On account of the number of circuit variables affecting reverse recovery voltage, no allowance for reverse recovery loss has been made in these ratings. The following procedure is recommended for use where it is necessary to include reverse recovery loss.

# **Determination by Measurement**

From waveforms of recovery current obtained from a high frequency shunt (see Note 1) and reverse voltage present during recovery, an instantaneous reverse recovery loss waveform must be constructed. Let the area under this waveform be A joules per pulse. A new case temperature can then be evaluated from:

$$T_{CASE}$$

(new) =  $T_{CASE}$  (original) –  $A\left(\frac{r_t \cdot 10^6}{t} + R_{th} \times f\right)$

where  $r_t = 3.47 \times 10^{-4} \sqrt{t}$

t = duration of reverse recovery loss per pulse in microseconds

A = Area under reverse loss waveform per pulse in joules (W.S.)

f = rated frequency at the original case temperature

The total dissipation is now given by

$W_{(TOT)} = W_{(original)} + A \times f$

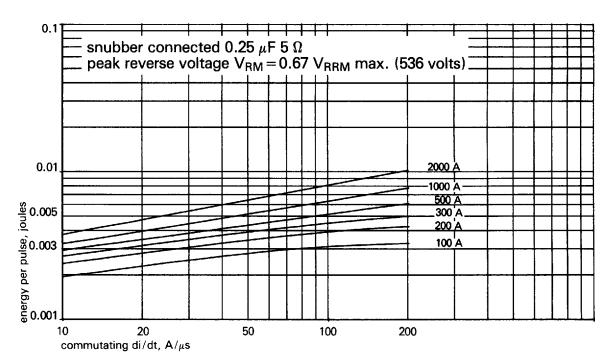

### (b) **Design Method**

In circumstances where it is not possible to measure voltage and current conditions, or for design purposes, the additional losses may be estimated from figure 7. A typical R-C snubber network is connected across the thyristor to control the transient reverse voltage waveform.

Let E be the value of energy per reverse cycle in joules (figure 7).

Let f be the operating frequency in Hz

then  $T_{CASE}$  new =  $T_{CASE}$  original –  $ER_{th} \times f$ where T<sub>CASE</sub> new is the required maximum case temperature

and T<sub>CASE</sub> original is the case temperature given with the frequency ratings.

# **GATE DRIVE**

The recommended gate drive is 20 V, 20 ohms with a short-circuit current rise time of not more than 1 us. This gate drive must be applied when using the full di/dt capability of the device.

### 5. THE DV/DT SUPPRESSION NETWORK

The effect of a conventional resistor-capacitor snubber of 0.25 µF 5 ohms has been included in these ratings and all rating di/dt values apply to the circuit external to the thyristor and its suppression network.

# **Snubber Network Values**

A series connected C-R filter may be required across the anode to cathode terminals of the thyristor for the purpose of reducing off-state voltage overshoot.

The optimum values for C and R depend partly on the circuits connected to the thyristor. For most applications the snubber design values should not exceed a maximum of 0.25 µF or a minimum of 5 ohms. Please consult Westcode for values outside these limits.

### 6. NOTE 1

# **REVERSE RECOVERY LOSS BY** MEASUREMENT

This thyristor has a low reverse recovered charge and peak reverse recovery current. When measuring the charge care must be taken to ensure that:

- (a) a.c. coupled devices such as current transformers are not affected by prior passage of high amplitude forward current.

- (b) The measuring oscilloscope has adequate dynamic range — typically 100 screen heights to cope with the initial forward current without overload.

Figure 1 Frequency v. pulse width

Figure 3 Frequency v. pulse width

Figure 2 Frequency v. pulse width

Figure 4 Frequency v. pulse width

Figure 5 Energy/pulse v. pulse width

Figure 6 Energy/pulse v. pulse width

Figure 7 Max. reverse recovery energy loss per pulse at 125°C junction temperature and  $V_{RM} = 536$  volts.

Figure 8 Frequency v. pulse width

100 1

10

1

0.1

frequency, KHz 0.0 10.0

0.01

sine wave

0.1 pulse width, m.secs Figure 10 Frequency v. pulse width

Figure 9 Energy/pulse v. pulse width

Typical recovered Figure 11 charge at 125°C junction temperature

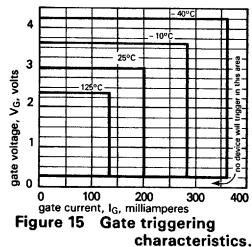

Figure 14 Gate characteristics at 25°C junction temperature

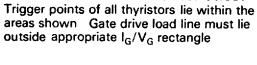

Figure 16 Limit on-state current

In the interest of product improvement, Westcode reserves the right to change specifications at any time without notice.

# **WESTCODE SEMICONDUCTORS LTD**

P.O. Box 57 Chippenham Wiltshire SN15 1JL England Telephone Chippenham (0249) 654141 Telex 44751

HAWKER SIDDELEY

Westinghouse Brake and Signal Co. Ltd.